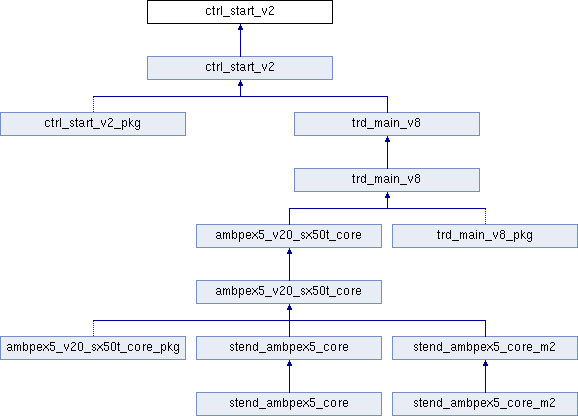

Граф наследования:ctrl_start_v2:

Processes | |

| pr_clk | ( b_clk , fmode ) |

| pr_cnt_clk | ( reset , start_a , fdiv_we , fmode , clki ) |

| pr_clk_cnt_z1 | ( clki ) |

| pr_clko_cnt | ( clki , clk_cnt , clk_div1 , clk_cnt_half ) |

| pr_clko | ( mode0 , b_clk , clko_cnt ) |

| pr_starto | ( mode0 , b_start , start_s ) |

| pr_start_i | ( stmode , b_start , start_prog ) |

| pr_stop_i | ( stmode , b_start , mode0( 5 ) ) |

| pr_start_a_tr | ( mode0 , start_a_tr_clr , start_i1 ) |

| pr_start_a_tr1 | ( b_clk ) |

| pr_start_a_tr_clr | ( mode0 , prog_start , start_a_tr1 , stop_i1 ) |

| pr_start_si | ( clko ) |

| pr_clk_clr | ( reset , clk_clr_cl0 , start_a ) |

| pr_clk_cl0 | ( reset , b_clk( 0 ) ) |

| pr_clk_clr_block | ( reset , b_clk( 0 ) ) |

Signals | |

| clki | std_logic |

| clko_cnt | std_logic |

| clko | std_logic |

| clk_cnt | std_logic_vector ( 15 downto 0 ) |

| clk_cnt_z1 | std_logic |

| clk_cnt_z | std_logic |

| clk_cnt_half | std_logic |

| clk_div1 | std_logic |

| xcnt0 | std_logic_vector ( 15 downto 0 ) |

| xcnt1 | std_logic_vector ( 15 downto 0 ) |

| xcnt2 | std_logic_vector ( 15 downto 0 ) |

| xcnt0_z | std_logic |

| xcnt1_z | std_logic |

| xcnt2_z | std_logic |

| start_a | std_logic |

| start_a_tr1 | std_logic |

| start_a_tr | std_logic |

| start_a_tr_clr | std_logic |

| start_i1 | std_logic |

| start_i | std_logic |

| stop_i1 | std_logic |

| stop_i | std_logic |

| start_si | std_logic |

| start_s | std_logic |

| start_cnt0 | std_logic |

| start_cnt12 | std_logic |

| xcnt1_start | std_logic |

| xcnt2_start | std_logic |

| adcen | std_logic |

| start_o | std_logic |

| clk_clr | std_logic |

| clk_clr_cl0 | std_logic |

| clk_clr_block | std_logic |

| start_prog | std_logic |

| prog_start | std_logic |

Подробное описание

См. определение в файле ctrl_start_v2.vhd строка 114

Объявления и описания членов класса находятся в файле:

- adm/rtl/ctrl_start_v2.vhd

1.7.4

1.7.4