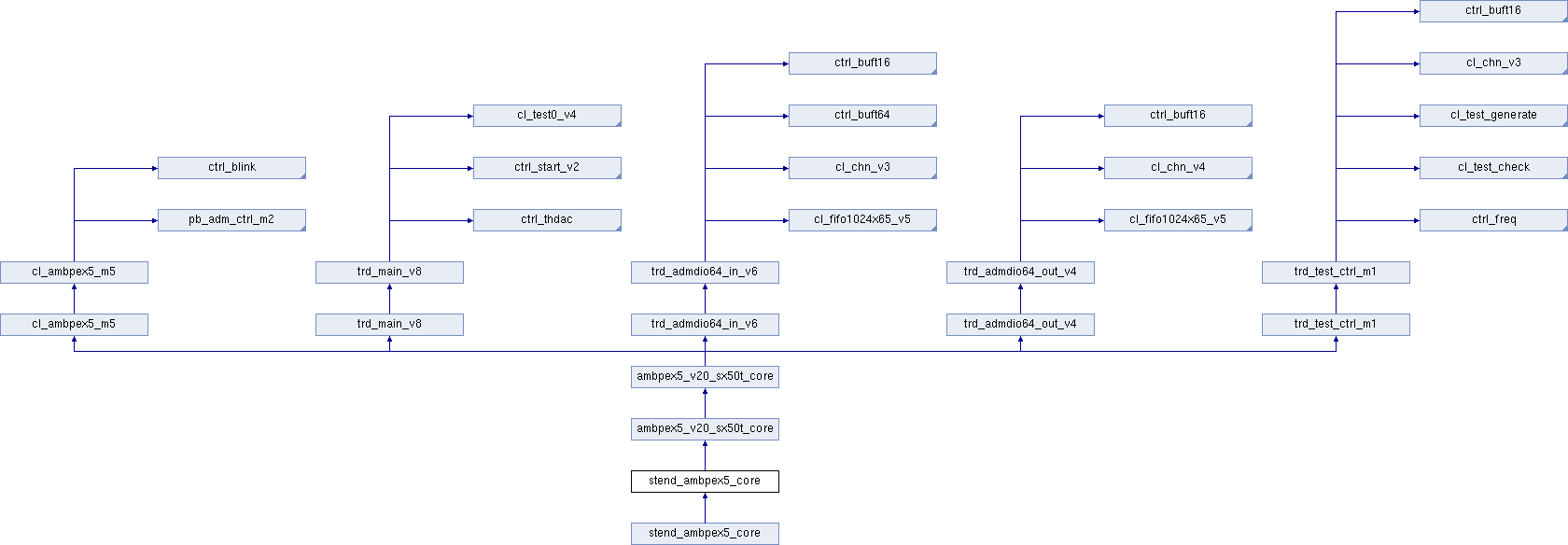

Граф наследования:stend_ambpex5_core:

Components | |

| xilinx_pcie_2_0_rport_v6 | |

Signals | |

| clk250 | std_logic := ' 0 ' |

| clk250p | std_logic |

| clk250n | std_logic |

| clk100 | std_logic := ' 0 ' |

| reset | std_logic |

| txp | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| txn | std_logic_vector ( 7 downto 0 ) := ( others = > ' 1 ' ) |

| rxp | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| rxn | std_logic_vector ( 7 downto 0 ) := ( others = > ' 1 ' ) |

| rp_txp | std_logic_vector ( 0 downto 0 ) := ( others = > ' 0 ' ) |

| rp_txn | std_logic_vector ( 0 downto 0 ) := ( others = > ' 1 ' ) |

| rp_rxp | std_logic_vector ( 0 downto 0 ) := ( others = > ' 0 ' ) |

| rp_rxn | std_logic_vector ( 0 downto 0 ) := ( others = > ' 1 ' ) |

| tp | std_logic_vector ( 3 downto 1 ) |

| led1 | std_logic |

| led2 | std_logic |

| led3 | std_logic |

| led4 | std_logic |

Component Instantiations | |

| amb | ambpex5_v20_sx50t_core <Entity ambpex5_v20_sx50t_core> |

| rp | xilinx_pcie_2_0_rport_v6 |

Подробное описание

См. определение в файле stend_ambpex5_core.vhd строка 26

Объявления и описания членов класса находятся в файле:

- testbench/stend_ambpex5_core.vhd

1.7.4

1.7.4