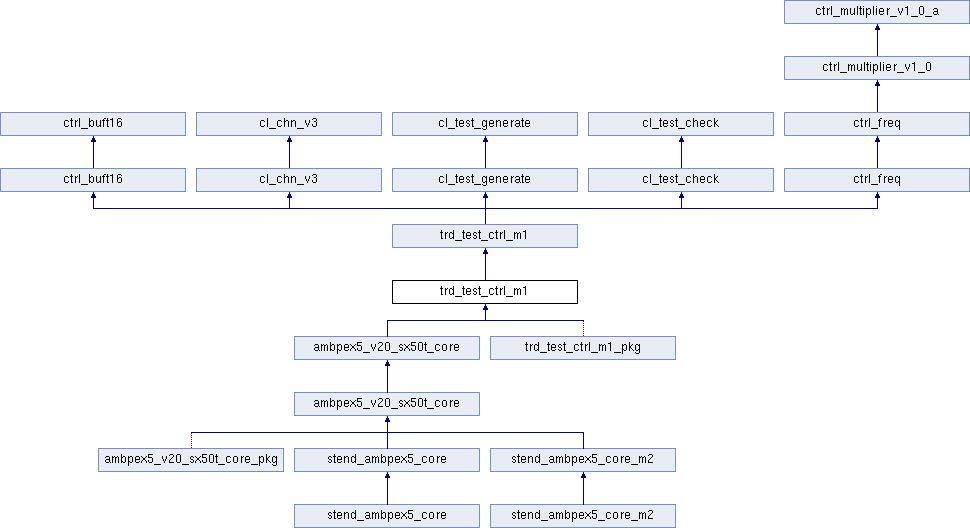

Граф наследования:trd_test_ctrl_m1:

Architectures | |

| trd_test_ctrl_m1 | Architecture |

Libraries | |

| ieee | |

| unisim | |

| work | |

Packages | |

| std_logic_1164 | |

| vcomponents | |

| cl_chn_v3_pkg | Package <cl_chn_v3_pkg> |

| adm2_pkg | Package <adm2_pkg> |

| cl_test_generate_pkg | Package <cl_test_generate_pkg> |

| cl_test_check_pkg | Package <cl_test_check_pkg> |

| ctrl_freq_pkg | Package <ctrl_freq_pkg> |

Generics | |

| SystemFreq | integer := 500 |

Ports | |

| reset | in std_logic |

| clk | in std_logic |

| cmd_data_in | in std_logic_vector ( 15 downto 0 ) |

| cmd | in bl_cmd |

| cmd_data_out | out std_logic_vector ( 15 downto 0 ) |

| cmd_data_out2 | out std_logic_vector ( 15 downto 0 ) |

| bx_irq | out std_logic |

| bx_drq | out bl_drq |

| mode0 | out std_logic_vector ( 15 downto 0 ) |

| mode1 | out std_logic_vector ( 15 downto 0 ) |

| mode2 | out std_logic_vector ( 15 downto 0 ) |

| mode3 | out std_logic_vector ( 15 downto 0 ) |

| di_clk | out std_logic |

| di_data | out std_logic_vector ( 63 downto 0 ) |

| di_data_we | out std_logic |

| di_flag_wr | in bl_fifo_flag |

| di_fifo_rst | in std_logic |

| di_mode1 | in std_logic_vector ( 15 downto 0 ) |

| di_start | in std_logic |

| do_clk | out std_logic |

| do_data | in std_logic_vector ( 63 downto 0 ) |

| do_data_cs | out std_logic |

| do_flag_rd | in bl_fifo_flag |

| do_fifo_rst | in std_logic |

| do_mode1 | in std_logic_vector ( 15 downto 0 ) |

| do_start | in std_logic |

| clk_sys | in std_logic := ' 0 ' |

| clk_check0 | in std_logic := ' 0 ' |

| clk_check1 | in std_logic := ' 0 ' |

| clk_check2 | in std_logic := ' 0 ' |

Подробное описание

См. определение в файле trd_test_ctrl_m1.vhd строка 120

Объявления и описания членов класса находятся в файле:

- adm/trd_test_ctrl/trd_test_ctrl_m1.vhd

1.7.4

1.7.4