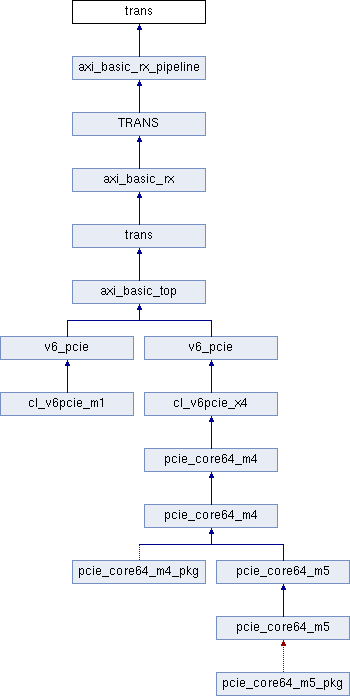

Граф наследования:trans:

Processes | |

| PROCESS_16 | ( USER_CLK ) |

| PROCESS_17 | ( USER_CLK ) |

| PROCESS_18 | ( USER_CLK ) |

| PROCESS_19 | ( USER_CLK ) |

| PROCESS_20 | ( USER_CLK ) |

| PROCESS_21 | ( USER_CLK ) |

| PROCESS_22 | ( USER_CLK ) |

| PROCESS_23 | ( USER_CLK , USER_RST ) |

| PROCESS_24 | ( USER_CLK ) |

Signals | |

| is_sof | STD_LOGIC_VECTOR ( 4 DOWNTO 0 ) |

| is_sof_prev | STD_LOGIC_VECTOR ( 4 DOWNTO 0 ) |

| is_eof | STD_LOGIC_VECTOR ( 4 DOWNTO 0 ) |

| is_eof_prev | STD_LOGIC_VECTOR ( 4 DOWNTO 0 ) |

| reg_tstrb | STD_LOGIC_VECTOR ( C_STRB_WIDTH- 1 DOWNTO 0 ) |

| tstrb | STD_LOGIC_VECTOR ( C_STRB_WIDTH- 1 DOWNTO 0 ) |

| tstrb_prev | STD_LOGIC_VECTOR ( C_STRB_WIDTH- 1 DOWNTO 0 ) |

| reg_tlast | STD_LOGIC |

| rsrc_rdy_filtered | STD_LOGIC |

| trn_rd_DW_swapped | STD_LOGIC_VECTOR ( C_DATA_WIDTH- 1 DOWNTO 0 ) |

| trn_rd_prev | STD_LOGIC_VECTOR ( C_DATA_WIDTH- 1 DOWNTO 0 ) |

| data_hold | STD_LOGIC |

| data_prev | STD_LOGIC |

| trn_reof_prev | STD_LOGIC |

| trn_rrem_prev | STD_LOGIC_VECTOR ( C_REM_WIDTH- 1 DOWNTO 0 ) |

| trn_rsrc_rdy_prev | STD_LOGIC |

| trn_rsrc_dsc_prev | STD_LOGIC |

| trn_rsof_prev | STD_LOGIC |

| trn_rbar_hit_prev | STD_LOGIC_VECTOR ( 6 DOWNTO 0 ) |

| trn_rerrfwd_prev | STD_LOGIC |

| trn_recrc_err_prev | STD_LOGIC |

| null_mux_sel | STD_LOGIC |

| trn_in_packet | STD_LOGIC |

| dsc_flag | STD_LOGIC |

| dsc_detect | STD_LOGIC |

| reg_dsc_detect | STD_LOGIC |

| trn_rsrc_dsc_d | STD_LOGIC |

| m_axis_rx_tdata_xhdl0 | STD_LOGIC_VECTOR ( C_DATA_WIDTH- 1 DOWNTO 0 ) |

| m_axis_rx_tvalid_xhdl2 | STD_LOGIC |

| m_axis_rx_tuser_xhdl1 | STD_LOGIC_VECTOR ( 21 DOWNTO 0 ) |

| trn_rdst_rdy_xhdl4 | STD_LOGIC |

| mrd_lower | STD_LOGIC |

| mrd_lk_lower | STD_LOGIC |

| io_rdwr_lower | STD_LOGIC |

| cfg_rdwr_lower | STD_LOGIC |

| atomic_lower | STD_LOGIC |

| np_pkt_lower | STD_LOGIC |

| mrd_upper | STD_LOGIC |

| mrd_lk_upper | STD_LOGIC |

| io_rdwr_upper | STD_LOGIC |

| cfg_rdwr_upper | STD_LOGIC |

| atomic_upper | STD_LOGIC |

| np_pkt_upper | STD_LOGIC |

| pkt_accepted | STD_LOGIC |

| reg_np_counter | STD_LOGIC_VECTOR ( 2 DOWNTO 0 ) |

Подробное описание

См. определение в файле axi_basic_rx_pipeline.vhd строка 123

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/source_virtex6/axi_basic_rx_pipeline.vhd

1.7.4

1.7.4