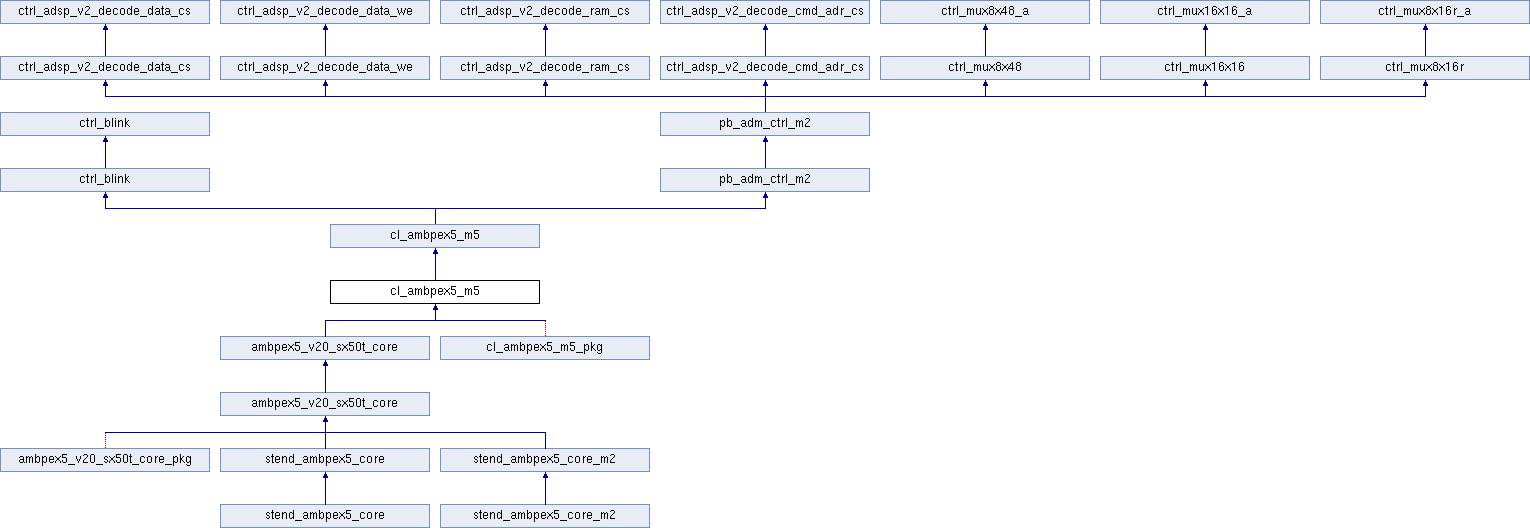

Граф наследования:cl_ambpex5_m5:

Architectures | |

| cl_ambpex5_m5 | Architecture |

Libraries | |

| ieee | |

| unisim | |

| work | |

Packages | |

| std_logic_1164 | |

| std_logic_arith | |

| std_logic_unsigned | |

| vcomponents | |

| adm2_pkg | Package <adm2_pkg> |

| pb_adm_ctrl_m2_pkg | Package <pb_adm_ctrl_m2_pkg> |

| ctrl_blink_pkg | Package <ctrl_blink_pkg> |

Generics | |

| BANDWIDTH | string := " optimized " |

| CLKFBOUT_MULT | integer := 16 |

| CLKFBOUT_PHASE | real := 0.0 |

| CLKIN_PERIOD | real := 0.000 |

| CLKOUT0_DIVIDE | integer := 3 |

| CLKOUT0_DUTY_CYCLE | real := 0.5 |

| CLKOUT0_PHASE | real := 0.0 |

| CLKOUT1_DIVIDE | integer := 4 |

| CLKOUT1_DUTY_CYCLE | real := 0.5 |

| CLKOUT1_PHASE | real := 0.0 |

| CLKOUT2_DIVIDE | integer := 1 |

| CLKOUT2_DUTY_CYCLE | real := 0.5 |

| CLKOUT2_PHASE | real := 0.0 |

| CLKOUT3_DIVIDE | integer := 1 |

| CLKOUT3_DUTY_CYCLE | real := 0.5 |

| CLKOUT3_PHASE | real := 0.0 |

| CLKOUT4_DIVIDE | integer := 1 |

| CLKOUT4_DUTY_CYCLE | real := 0.5 |

| CLKOUT4_PHASE | real := 0.0 |

| CLKOUT5_DIVIDE | integer := 1 |

| CLKOUT5_DUTY_CYCLE | real := 0.5 |

| CLKOUT5_PHASE | real := 0.0 |

| CLK_FEEDBACK | string := " clkfbout " |

| COMPENSATION | string := " system_synchronous " |

| DIVCLK_DIVIDE | integer := 5 |

| REF_JITTER | real := 0.100 |

| RESET_ON_LOSS_OF_LOCK | boolean := false |

| trd_rom | in std_logic_array_16xbl_trd_rom := ( others = > ( others = > ( others = > ' 0 ' ) ) ) |

| trd_in | in std_logic_vector ( 15 downto 0 ) := x " 0000 " |

| trd_st | in std_logic_vector ( 15 downto 0 ) := x " 0000 " |

| is_simulation | integer := 0 |

Ports | |

| txp | out std_logic_vector ( 7 downto 0 ) |

| txn | out std_logic_vector ( 7 downto 0 ) |

| rxp | in std_logic_vector ( 7 downto 0 ) |

| rxn | in std_logic_vector ( 7 downto 0 ) |

| mgt251_p | in std_logic |

| mgt251_n | in std_logic |

| bperst | in std_logic |

| p | out std_logic_vector ( 3 downto 1 ) |

| led_h1 | out std_logic |

| led_h2 | out std_logic |

| led_h3 | out std_logic |

| led_h4 | out std_logic |

| clk_out | out std_logic |

| reset_out | out std_logic |

| test_mode | in std_logic |

| clk30k | out std_logic |

| clk200_out | out std_logic |

| clk2_pll | out std_logic |

| clk3_pll | out std_logic |

| clk4_pll | out std_logic |

| clk5_pll | out std_logic |

| clk_lock_out | out std_logic |

| trd_host_adr | out std_logic_vector ( 15 downto 0 ) |

| trd_host_data | out std_logic_array_16x64 |

| trd_host_cmd_data | out std_logic_array_16x16 |

| trd_host_cmd | out std_logic_array_16xbl_cmd |

| trd_data | in std_logic_array_16x64 := ( others = > ( others = > ' 0 ' ) ) |

| trd_cmd_data | in std_logic_array_16x16 := ( others = > ( others = > ' 0 ' ) ) |

| trd_drq | in std_logic_array_16xbl_drq := ( others = > ( others = > ' 0 ' ) ) |

| trd_main_drq | in std_logic_array_16xbl_drq := ( others = > ( others = > ' 0 ' ) ) |

| trd_main_sel_drq | in std_logic_array_16x6 := ( others = > ( others = > ' 0 ' ) ) |

| trd_reset_fifo | in std_logic_array_16xbl_reset_fifo := ( others = > ' 0 ' ) |

| trd_main_irq | in std_logic_array_16xbl_irq := ( others = > ' 0 ' ) |

Подробное описание

См. определение в файле cl_ambpex5_m5.vhd строка 169

Объявления и описания членов класса находятся в файле:

- adm/cl_ambpex5/top/cl_ambpex5_m5.vhd

1.7.4

1.7.4