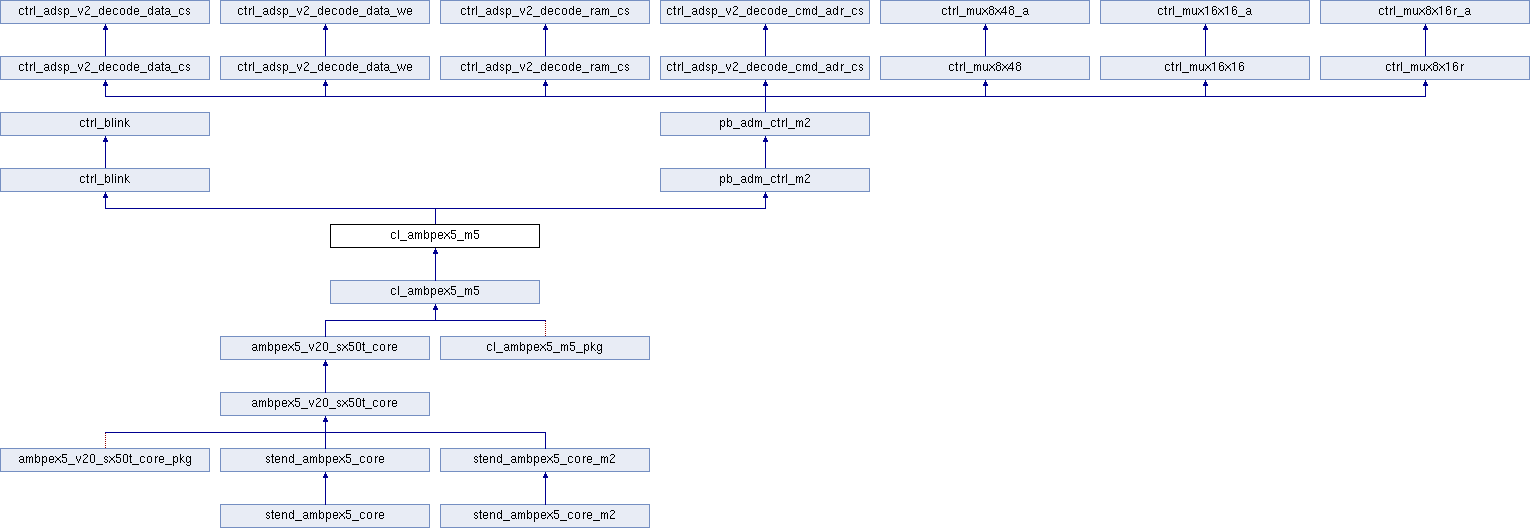

Граф наследования:cl_ambpex5_m5:

Components | |

| cl_adm_simulation | |

| pcie_core64_m2 | |

Signals | |

| mgt250 | std_logic |

| perst | std_logic |

| lc_adr | std_logic_vector ( 31 downto 0 ) |

| lc_host_data | std_logic_vector ( 63 downto 0 ) |

| lc_data | std_logic_vector ( 63 downto 0 ) |

| lc_wr | std_logic |

| lc_rd | std_logic |

| lc_dma_req | std_logic_vector ( 1 downto 0 ) |

| lc_irq | std_logic |

| irq1 | std_logic |

| dmar0 | std_logic |

| dmar1 | std_logic |

| dmar2 | std_logic |

| dmar3 | std_logic |

| trdi_host_data | std_logic_vector ( 63 downto 0 ) |

| dcm_rstp | std_logic |

| clk_lock | std_logic |

| clk250 | std_logic |

| clk200 | std_logic |

| clk200x | std_logic |

| clk266x | std_logic |

| clkfb | std_logic |

| clk30i | std_logic |

| cnt30k0 | std_logic |

| cnt30k1 | std_logic |

| cnt30k2 | std_logic |

| cnt30i0 | std_logic |

| cnt30i1 | std_logic |

| cnt30i2 | std_logic |

| cnt30ce0 | std_logic |

| cnt30ce1 | std_logic |

| cnt30ce2 | std_logic |

| cnt30start | std_logic |

| cnt30start1 | std_logic |

| trdi_host_cmd | std_logic_array_16xbl_cmd |

| clk | std_logic := ' 0 ' |

| reset | std_logic |

| pcie_link_up | std_logic |

| pcie_lstatus | std_logic_vector ( 15 downto 0 ) |

| px | std_logic_vector ( 7 downto 0 ) |

| trd4_host_data | std_logic_vector ( 63 downto 0 ) |

Attributes | |

| period | string |

| period | " 250 MHz " |

| buffer_type | string |

| clock_buffer | string |

| buffer_type | " none " |

| clock_buffer | " none " |

| syn_keep | boolean |

| syn_keep | true |

Component Instantiations | |

| xclk200 | bufg |

| xmgtclk | IBUFDS |

| xmperst | ibuf |

| pcie | pcie_core64_m2 |

| blink | ctrl_blink <Entity ctrl_blink> |

| ad | pb_adm_ctrl_m2 <Entity pb_adm_ctrl_m2> |

| ctrl | cl_adm_simulation |

| xfd | fd |

| xcnt0 | srlc32e |

| xcnt1 | srlc32e |

| xcnt2 | srlc32e |

Подробное описание

См. определение в файле cl_ambpex5_m5.vhd строка 289

Объявления и описания членов класса находятся в файле:

- adm/cl_ambpex5/top/cl_ambpex5_m5.vhd

1.7.4

1.7.4