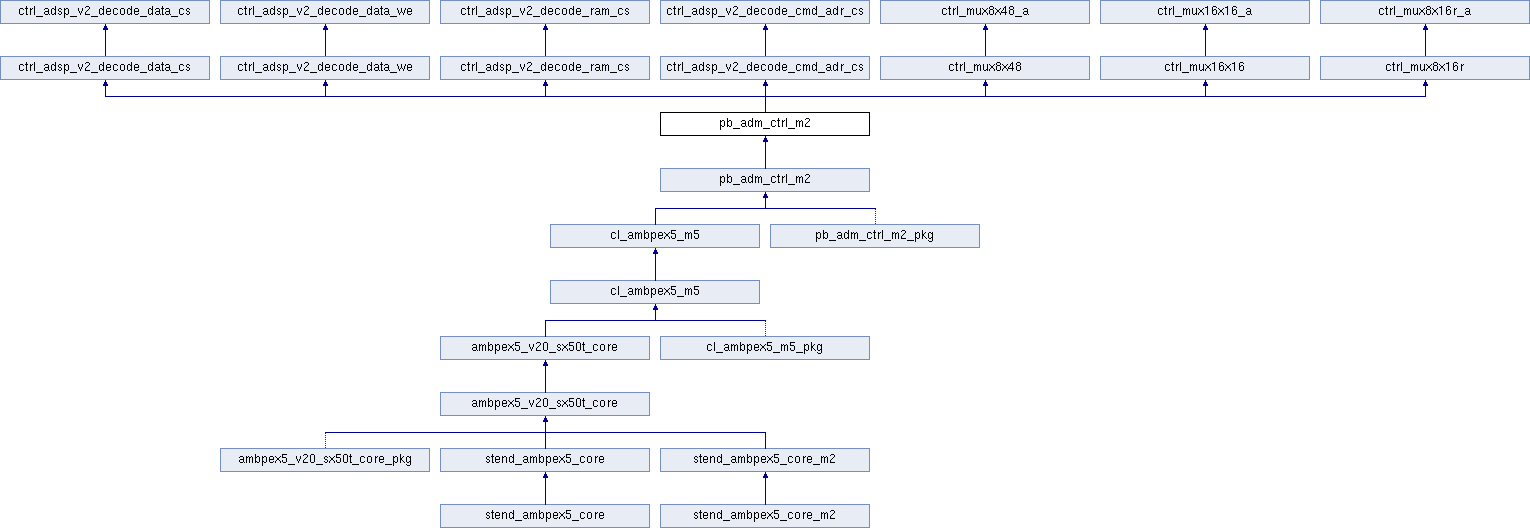

Граф наследования:pb_adm_ctrl_m2:

Functions | |

| bit_vector | conv_rom ( rom: in bl_trd_rom , mode: in integer ) |

| string | conv_string ( rom: in bl_trd_rom , mode: in integer ) |

Processes | |

| pr_ms2 | ( reset , clk ) |

| pr_adr_in | ( clk ) |

| pr_bl_adr_out | ( clk ) |

| pr_addra | ( clk ) |

| pr_dpram_en | ( clk ) |

| pr_sel_cmd_data | ( adr1 , cmd0_adr , cmd1_adr , cmd2_adr , cmd3_adr , cmd4_adr , cmd5_adr , cmd6_adr , cmd7_adr ) |

| pr_cmd_adr | ( reset , clk ) |

| pr_adr_we1 | ( clk ) |

| pr_irq | ( clk ) |

| pr_flag4 | ( clk ) |

| pr_mux_sel | ( clk ) |

| pr_flag_data_we4 | ( clk ) |

| pr_main_mode2 | ( clk ) |

Components | |

| ctrl_dram256x16_v2 | |

| RAMB16_S18 | |

| ctrl_adsp_v2_decode_data_cs | <Entity ctrl_adsp_v2_decode_data_cs> |

| ctrl_adsp_v2_decode_data_in_cs | <Entity ctrl_adsp_v2_decode_data_in_cs> |

| ctrl_adsp_v2_decode_ram_cs | <Entity ctrl_adsp_v2_decode_ram_cs> |

| ctrl_adsp_v2_decode_data_we | <Entity ctrl_adsp_v2_decode_data_we> |

| ctrl_adsp_v2_decode_cmd_adr_cs | <Entity ctrl_adsp_v2_decode_cmd_adr_cs> |

| ctrl_mux8x48 | <Entity ctrl_mux8x48> |

| ctrl_mux16x16 | <Entity ctrl_mux16x16> |

| ctrl_mux8x16r | <Entity ctrl_mux8x16r> |

Constants | |

| rom_init_00 | bit_vector ( 255 downto 0 ) := conv_rom ( rom0 , 0 ) |

| rom_init_01 | bit_vector ( 255 downto 0 ) := conv_rom ( rom0 , 1 ) |

| rom_init_02 | bit_vector ( 255 downto 0 ) := conv_rom ( rom1 , 0 ) |

| rom_init_03 | bit_vector ( 255 downto 0 ) := conv_rom ( rom1 , 1 ) |

| rom_init_04 | bit_vector ( 255 downto 0 ) := conv_rom ( rom2 , 0 ) |

| rom_init_05 | bit_vector ( 255 downto 0 ) := conv_rom ( rom2 , 1 ) |

| rom_init_06 | bit_vector ( 255 downto 0 ) := conv_rom ( rom3 , 0 ) |

| rom_init_07 | bit_vector ( 255 downto 0 ) := conv_rom ( rom3 , 1 ) |

| rom_init_08 | bit_vector ( 255 downto 0 ) := conv_rom ( rom4 , 0 ) |

| rom_init_09 | bit_vector ( 255 downto 0 ) := conv_rom ( rom4 , 1 ) |

| rom_init_0A | bit_vector ( 255 downto 0 ) := conv_rom ( rom5 , 0 ) |

| rom_init_0B | bit_vector ( 255 downto 0 ) := conv_rom ( rom5 , 1 ) |

| rom_init_0C | bit_vector ( 255 downto 0 ) := conv_rom ( rom6 , 0 ) |

| rom_init_0D | bit_vector ( 255 downto 0 ) := conv_rom ( rom6 , 1 ) |

| rom_init_0E | bit_vector ( 255 downto 0 ) := conv_rom ( rom7 , 0 ) |

| rom_init_0F | bit_vector ( 255 downto 0 ) := conv_rom ( rom7 , 1 ) |

| str_init_00 | string := conv_string ( rom0 , 0 ) |

| str_init_01 | string := conv_string ( rom0 , 1 ) |

| str_init_02 | string := conv_string ( rom1 , 0 ) |

| str_init_03 | string := conv_string ( rom1 , 1 ) |

| str_init_04 | string := conv_string ( rom2 , 0 ) |

| str_init_05 | string := conv_string ( rom2 , 1 ) |

| str_init_06 | string := conv_string ( rom3 , 0 ) |

| str_init_07 | string := conv_string ( rom3 , 1 ) |

| str_init_08 | string := conv_string ( rom4 , 0 ) |

| str_init_09 | string := conv_string ( rom4 , 1 ) |

| str_init_0A | string := conv_string ( rom5 , 0 ) |

| str_init_0B | string := conv_string ( rom5 , 1 ) |

| str_init_0C | string := conv_string ( rom6 , 0 ) |

| str_init_0D | string := conv_string ( rom6 , 1 ) |

| str_init_0E | string := conv_string ( rom7 , 0 ) |

| str_init_0F | string := conv_string ( rom7 , 1 ) |

Signals | |

| ms1 | std_logic |

| rd2 | std_logic |

| rd1 | std_logic |

| wrl2 | std_logic |

| wrl1 | std_logic |

| adr2 | std_logic_vector ( 6 downto 0 ) |

| adr1 | std_logic_vector ( 6 downto 0 ) |

| data2 | std_logic_vector ( 63 downto 0 ) |

| rd2z | std_logic |

| data_out2 | std_logic_vector ( 63 downto 0 ) |

| cmd_data2 | std_logic_vector ( 15 downto 0 ) |

| rom_data2 | std_logic_vector ( 15 downto 0 ) |

| dpram_en | std_logic |

| sinit | std_logic |

| dpram_en0 | std_logic |

| addra | std_logic_vector ( 9 downto 0 ) |

| addra2 | std_logic_vector ( 15 downto 0 ) |

| dpram_cs2 | std_logic |

| bl_status_cs | std_logic_vector ( 7 downto 0 ) |

| bl_data_cs | std_logic_vector ( 7 downto 0 ) |

| bl_cmd_data_cs | std_logic_vector ( 7 downto 0 ) |

| bl_data_we | std_logic_vector ( 7 downto 0 ) |

| bl_cmd_adr_we | std_logic_vector ( 7 downto 0 ) |

| bl_cmd_adr_we1 | std_logic_vector ( 7 downto 0 ) |

| bl_cmd_data_we | std_logic_vector ( 7 downto 0 ) |

| bl_cmd_data_we1 | std_logic_vector ( 7 downto 0 ) |

| ram_cs2 | std_logic |

| ram_cs1 | std_logic |

| rom_cs2 | std_logic |

| data_in_cs2 | std_logic |

| data_in_cs2_0 | std_logic |

| cmd_adr_cs2 | std_logic |

| cmd3_adr | std_logic_vector ( 15 downto 0 ) |

| cmd2_adr | std_logic_vector ( 15 downto 0 ) |

| cmd1_adr | std_logic_vector ( 15 downto 0 ) |

| cmd0_adr | std_logic_vector ( 15 downto 0 ) |

| cmd7_adr | std_logic_vector ( 15 downto 0 ) |

| cmd6_adr | std_logic_vector ( 15 downto 0 ) |

| cmd5_adr | std_logic_vector ( 15 downto 0 ) |

| cmd4_adr | std_logic_vector ( 15 downto 0 ) |

| rom_di | std_logic_vector ( 15 downto 0 ) |

| sel_cmd_data | std_logic |

| sel_cmd_ram | std_logic |

| sel_cmd_rom | std_logic |

| flyby1 | std_logic |

| ram_rom_cs | std_logic |

| en_ram | std_logic |

| mh | std_logic_vector ( 63 downto 0 ) |

| mg | std_logic_vector ( 63 downto 0 ) |

| mf | std_logic_vector ( 63 downto 0 ) |

| me | std_logic_vector ( 63 downto 0 ) |

| md | std_logic_vector ( 63 downto 0 ) |

| mc | std_logic_vector ( 63 downto 0 ) |

| mb | std_logic_vector ( 63 downto 0 ) |

| ma | std_logic_vector ( 63 downto 0 ) |

| mah | std_logic_vector ( 15 downto 0 ) |

| mag | std_logic_vector ( 15 downto 0 ) |

| maf | std_logic_vector ( 15 downto 0 ) |

| mae | std_logic_vector ( 15 downto 0 ) |

| mad | std_logic_vector ( 15 downto 0 ) |

| mac | std_logic_vector ( 15 downto 0 ) |

| mab | std_logic_vector ( 15 downto 0 ) |

| maa | std_logic_vector ( 15 downto 0 ) |

| nh | std_logic_vector ( 15 downto 0 ) |

| ng | std_logic_vector ( 15 downto 0 ) |

| nf | std_logic_vector ( 15 downto 0 ) |

| ne | std_logic_vector ( 15 downto 0 ) |

| nd | std_logic_vector ( 15 downto 0 ) |

| nc | std_logic_vector ( 15 downto 0 ) |

| nb | std_logic_vector ( 15 downto 0 ) |

| na | std_logic_vector ( 15 downto 0 ) |

| mux_sel | std_logic_vector ( 3 downto 0 ) |

| flyby2 | std_logic |

| flag_data_we | std_logic_vector ( 7 downto 0 ) |

| main_mode2_4 | std_logic := ' 0 ' |

| trd4i_host_data | std_logic_vector ( 63 downto 0 ) |

| flag_rd_block | std_logic_vector ( 15 downto 0 ) |

| flag_rd_repack | std_logic_vector ( 15 downto 0 ) |

| trd_repack_data | std_logic_array_16x64 := ( others = > ( others = > ' 0 ' ) ) |

| lc_data_i | std_logic_vector ( 63 downto 0 ) |

Attributes | |

| rom_style | string |

| rom_style | " block " |

| init_10 | string |

| init_11 | string |

| init_12 | string |

| init_13 | string |

| init_14 | string |

| init_15 | string |

| init_16 | string |

| init_17 | string |

| init_18 | string |

| init_19 | string |

| init_1A | string |

| init_1B | string |

| init_1C | string |

| init_1D | string |

| init_1E | string |

| init_1F | string |

| init_10 | str_init_00 |

| init_11 | str_init_01 |

| init_12 | str_init_02 |

| init_13 | str_init_03 |

| init_14 | str_init_04 |

| init_15 | str_init_05 |

| init_16 | str_init_06 |

| init_17 | str_init_07 |

| init_18 | str_init_08 |

| init_19 | str_init_09 |

| init_1A | str_init_0A |

| init_1B | str_init_0B |

| init_1C | str_init_0C |

| init_1D | str_init_0D |

| init_1E | str_init_0E |

| init_1F | str_init_0F |

Component Instantiations | |

| rom | RAMB16_S18 |

| xstatus | ctrl_adsp_v2_decode_data_cs <Entity ctrl_adsp_v2_decode_data_cs> |

| xdata | ctrl_adsp_v2_decode_data_cs <Entity ctrl_adsp_v2_decode_data_cs> |

| xcmd_data | ctrl_adsp_v2_decode_data_cs <Entity ctrl_adsp_v2_decode_data_cs> |

| xdata_we | ctrl_adsp_v2_decode_data_we <Entity ctrl_adsp_v2_decode_data_we> |

| xcmd_adr_we | ctrl_adsp_v2_decode_data_we <Entity ctrl_adsp_v2_decode_data_we> |

| xcmd_data_we | ctrl_adsp_v2_decode_data_we <Entity ctrl_adsp_v2_decode_data_we> |

| xcmd_ram | ctrl_adsp_v2_decode_ram_cs <Entity ctrl_adsp_v2_decode_ram_cs> |

| xcmd_rom | ctrl_adsp_v2_decode_ram_cs <Entity ctrl_adsp_v2_decode_ram_cs> |

| xcmd_adr | ctrl_adsp_v2_decode_cmd_adr_cs <Entity ctrl_adsp_v2_decode_cmd_adr_cs> |

| mux8 | ctrl_mux8x48 <Entity ctrl_mux8x48> |

| mux16 | ctrl_mux16x16 <Entity ctrl_mux16x16> |

| mux_cmd | ctrl_mux8x16r <Entity ctrl_mux8x16r> |

Подробное описание

См. определение в файле pb_adm_ctrl_m2.vhd строка 249

Объявления и описания членов класса находятся в файле:

- adm/cl_ambpex5/rtl/pb_adm_ctrl_m2.vhd

1.7.4

1.7.4