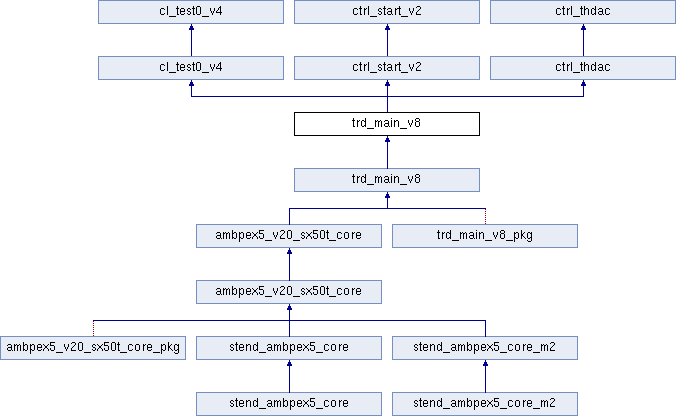

Граф наследования:trd_main_v8:

Processes | |

| pr_mode0 | ( reset , clk ) |

| pr_reg | ( rst , clk ) |

| pr_drq0 | ( c_sel_drq0 , b0_drq , b1_drq , b2_drq , b3_drq , b4_drq , b5_drq , b6_drq , b7_drq ) |

| pr_drq1 | ( c_sel_drq1 , b0_drq , b1_drq , b2_drq , b3_drq , b4_drq , b5_drq , b6_drq , b7_drq ) |

| pr_drq2 | ( c_sel_drq2 , b0_drq , b1_drq , b2_drq , b3_drq , b4_drq , b5_drq , b6_drq , b7_drq ) |

| pr_drq3 | ( c_sel_drq3 , b0_drq , b1_drq , b2_drq , b3_drq , b4_drq , b5_drq , b6_drq , b7_drq ) |

| pr_b0_irq | ( status , c_mask , c_inv , c_mode0 ) |

Components | |

| cl_test0_v1 | |

| ctrl_thdac | <Entity ctrl_thdac> |

Signals | |

| c_mode0 | std_logic_vector ( 15 downto 0 ) |

| c_inv | std_logic_vector ( 15 downto 0 ) |

| c_mask | std_logic_vector ( 15 downto 0 ) |

| c_thdac | std_logic_vector ( 11 downto 0 ) |

| thdac_start | std_logic |

| c_mux | std_logic_vector ( 1 downto 0 ) |

| do | std_logic_vector ( 63 downto 0 ) |

| c_synx | std_logic_vector ( 15 downto 0 ) |

| c_fmode | std_logic_vector ( 5 downto 0 ) |

| c_fdiv | std_logic_vector ( 15 downto 0 ) |

| fdiv_we | std_logic |

| c_stmode | std_logic_vector ( 15 downto 0 ) |

| irq_en | std_logic_vector ( 15 downto 0 ) |

| c_test_mode | std_logic |

| c_sel7 | std_logic_vector ( 1 downto 0 ) |

| c_sel6 | std_logic_vector ( 1 downto 0 ) |

| c_sel5 | std_logic_vector ( 1 downto 0 ) |

| c_sel4 | std_logic_vector ( 1 downto 0 ) |

| c_sel3 | std_logic_vector ( 1 downto 0 ) |

| c_sel2 | std_logic_vector ( 1 downto 0 ) |

| c_sel1 | std_logic_vector ( 1 downto 0 ) |

| c_sel0 | std_logic_vector ( 1 downto 0 ) |

| c_sel_drq3 | std_logic_vector ( 6 downto 0 ) |

| c_sel_drq2 | std_logic_vector ( 6 downto 0 ) |

| c_sel_drq1 | std_logic_vector ( 6 downto 0 ) |

| c_sel_drq0 | std_logic_vector ( 6 downto 0 ) |

| b0_irq | std_logic |

| b0_drq | bl_drq |

| rst | std_logic |

| i7_1 | std_logic |

| i6_1 | std_logic |

| i5_1 | std_logic |

| i4_1 | std_logic |

| i3_1 | std_logic |

| i2_1 | std_logic |

| i1_1 | std_logic |

| i0_1 | std_logic |

| i7_2 | std_logic |

| i6_2 | std_logic |

| i5_2 | std_logic |

| i4_2 | std_logic |

| i3_2 | std_logic |

| i2_2 | std_logic |

| i1_2 | std_logic |

| i0_2 | std_logic |

| i7_3 | std_logic |

| i6_3 | std_logic |

| i5_3 | std_logic |

| i4_3 | std_logic |

| i3_3 | std_logic |

| i2_3 | std_logic |

| i1_3 | std_logic |

| i0_3 | std_logic |

| i15_1 | std_logic |

| i14_1 | std_logic |

| i13_1 | std_logic |

| i12_1 | std_logic |

| i11_1 | std_logic |

| i10_1 | std_logic |

| i9_1 | std_logic |

| i8_1 | std_logic |

| i15_2 | std_logic |

| i14_2 | std_logic |

| i13_2 | std_logic |

| i12_2 | std_logic |

| i11_2 | std_logic |

| i10_2 | std_logic |

| i9_2 | std_logic |

| i8_2 | std_logic |

| i15_3 | std_logic |

| i14_3 | std_logic |

| i13_3 | std_logic |

| i12_3 | std_logic |

| i11_3 | std_logic |

| i10_3 | std_logic |

| i9_3 | std_logic |

| i8_3 | std_logic |

| status | std_logic_vector ( 15 downto 0 ) |

| th_rdy | std_logic |

| data_csp | std_logic |

| drq3i | bl_drq |

| drq2i | bl_drq |

| drq1i | bl_drq |

| drq0i | bl_drq |

| fifo_rst | std_logic |

| synx_test_mode | std_logic |

| reg_synx_in | std_logic_vector ( 15 downto 0 ) |

| bx_clki | std_logic |

Component Instantiations | |

| d_test0 | cl_test0_v4 <Entity cl_test0_v4> |

| start | ctrl_start_v2 <Entity ctrl_start_v2> |

| thdac | ctrl_thdac <Entity ctrl_thdac> |

Подробное описание

См. определение в файле trd_main_v8.vhd строка 379

Объявления и описания членов класса находятся в файле:

- adm/main/trd_main_v8.vhd

1.7.4

1.7.4