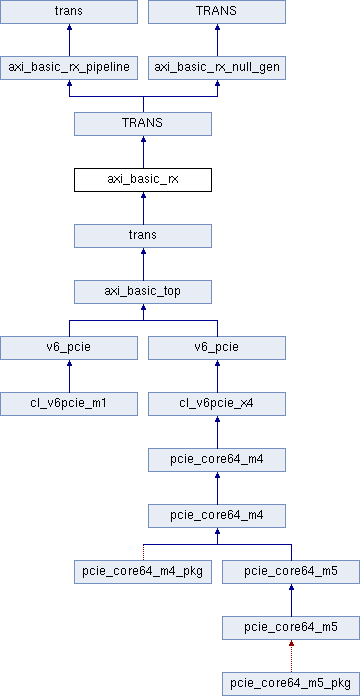

Граф наследования:axi_basic_rx:

Architectures | |

| TRANS | Architecture |

Libraries | |

| ieee | |

Packages | |

| std_logic_1164 | |

| std_logic_unsigned | |

Generics | |

| C_DATA_WIDTH | integer := 128 |

| C_FAMILY | string := " x7 " |

| C_ROOT_PORT | boolean := false |

| C_PM_PRIORITY | boolean := false |

| TCQ | integer := 1 |

| C_REM_WIDTH | integer := 1 |

| C_STRB_WIDTH | integer := 4 |

Ports | |

| M_AXIS_RX_TDATA | out std_logic_vector ( c_data_width- 1 downto 0 ) := ( others = > ' 0 ' ) |

| M_AXIS_RX_TVALID | out std_logic := ' 0 ' |

| M_AXIS_RX_TREADY | in std_logic := ' 0 ' |

| M_AXIS_RX_TSTRB | out std_logic_vector ( c_strb_width- 1 downto 0 ) := ( others = > ' 0 ' ) |

| M_AXIS_RX_TLAST | out std_logic := ' 0 ' |

| M_AXIS_RX_TUSER | out std_logic_vector ( 21 downto 0 ) := ( others = > ' 0 ' ) |

| TRN_RD | in std_logic_vector ( c_data_width- 1 downto 0 ) := ( others = > ' 0 ' ) |

| TRN_RSOF | in std_logic := ' 0 ' |

| TRN_REOF | in std_logic := ' 0 ' |

| TRN_RSRC_RDY | in std_logic := ' 0 ' |

| TRN_RDST_RDY | out std_logic := ' 0 ' |

| TRN_RSRC_DSC | in std_logic := ' 0 ' |

| TRN_RREM | in std_logic_vector ( c_rem_width- 1 downto 0 ) := ( others = > ' 0 ' ) |

| TRN_RERRFWD | in std_logic := ' 0 ' |

| TRN_RBAR_HIT | in std_logic_vector ( 6 downto 0 ) := ( others = > ' 0 ' ) |

| TRN_RECRC_ERR | in std_logic := ' 0 ' |

| NP_COUNTER | out std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| USER_CLK | in std_logic := ' 0 ' |

| USER_RST | in std_logic := ' 0 ' |

Подробное описание

См. определение в файле axi_basic_rx.vhd строка 72

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/source_virtex6/axi_basic_rx.vhd

1.7.4

1.7.4