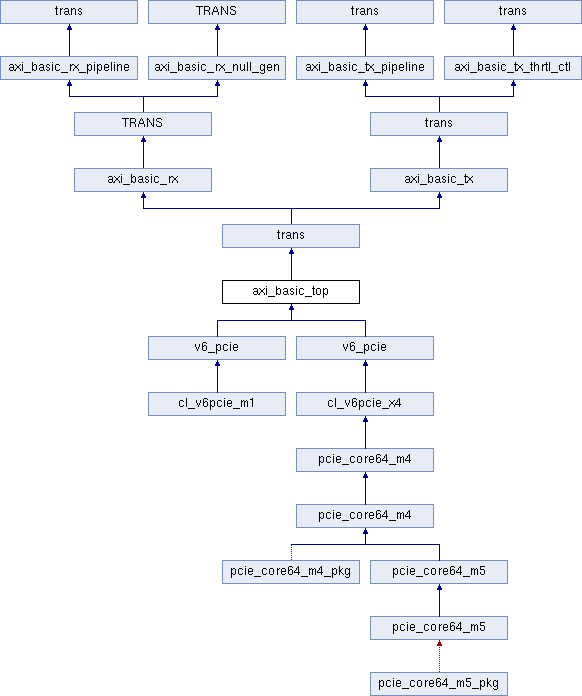

Граф наследования:axi_basic_top:

Architectures | |

| trans | Architecture |

Libraries | |

| ieee | |

Packages | |

| std_logic_1164 | |

| std_logic_unsigned | |

Generics | |

| C_DATA_WIDTH | integer := 128 |

| C_FAMILY | string := " x7 " |

| C_ROOT_PORT | boolean := false |

| C_PM_PRIORITY | boolean := false |

| TCQ | integer := 1 |

| C_REM_WIDTH | integer := 1 |

| C_STRB_WIDTH | integer := 4 |

Ports | |

| s_axis_tx_tdata | in std_logic_vector ( c_data_width- 1 downto 0 ) := ( others = > ' 0 ' ) |

| s_axis_tx_tvalid | in std_logic := ' 0 ' |

| s_axis_tx_tready | out std_logic := ' 0 ' |

| s_axis_tx_tstrb | in std_logic_vector ( c_strb_width- 1 downto 0 ) := ( others = > ' 0 ' ) |

| s_axis_tx_tlast | in std_logic := ' 0 ' |

| s_axis_tx_tuser | in std_logic_vector ( 3 downto 0 ) := ( others = > ' 0 ' ) |

| m_axis_rx_tdata | out std_logic_vector ( c_data_width- 1 downto 0 ) := ( others = > ' 0 ' ) |

| m_axis_rx_tvalid | out std_logic := ' 0 ' |

| m_axis_rx_tready | in std_logic := ' 0 ' |

| m_axis_rx_tstrb | out std_logic_vector ( c_strb_width- 1 downto 0 ) := ( others = > ' 0 ' ) |

| m_axis_rx_tlast | out std_logic := ' 0 ' |

| m_axis_rx_tuser | out std_logic_vector ( 21 downto 0 ) := ( others = > ' 0 ' ) |

| user_turnoff_ok | in std_logic := ' 0 ' |

| user_tcfg_gnt | in std_logic := ' 0 ' |

| trn_td | out std_logic_vector ( c_data_width- 1 downto 0 ) := ( others = > ' 0 ' ) |

| trn_tsof | out std_logic := ' 0 ' |

| trn_teof | out std_logic := ' 0 ' |

| trn_tsrc_rdy | out std_logic := ' 0 ' |

| trn_tdst_rdy | in std_logic := ' 0 ' |

| trn_tsrc_dsc | out std_logic := ' 0 ' |

| trn_trem | out std_logic_vector ( c_rem_width- 1 downto 0 ) := ( others = > ' 0 ' ) |

| trn_terrfwd | out std_logic := ' 0 ' |

| trn_tstr | out std_logic := ' 0 ' |

| trn_tbuf_av | in std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| trn_tecrc_gen | out std_logic := ' 0 ' |

| trn_rd | in std_logic_vector ( c_data_width- 1 downto 0 ) := ( others = > ' 0 ' ) |

| trn_rsof | in std_logic := ' 0 ' |

| trn_reof | in std_logic := ' 0 ' |

| trn_rsrc_rdy | in std_logic := ' 0 ' |

| trn_rdst_rdy | out std_logic := ' 0 ' |

| trn_rsrc_dsc | in std_logic := ' 0 ' |

| trn_rrem | in std_logic_vector ( c_rem_width- 1 downto 0 ) := ( others = > ' 0 ' ) |

| trn_rerrfwd | in std_logic := ' 0 ' |

| trn_rbar_hit | in std_logic_vector ( 6 downto 0 ) := ( others = > ' 0 ' ) |

| trn_recrc_err | in std_logic := ' 0 ' |

| trn_tcfg_req | in std_logic := ' 0 ' |

| trn_tcfg_gnt | out std_logic := ' 0 ' |

| trn_lnk_up | in std_logic := ' 0 ' |

| cfg_pcie_link_state | in std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| cfg_pm_send_pme_to | in std_logic := ' 0 ' |

| cfg_pmcsr_powerstate | in std_logic_vector ( 1 downto 0 ) := ( others = > ' 0 ' ) |

| trn_rdllp_data | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| trn_rdllp_src_rdy | in std_logic := ' 0 ' |

| cfg_to_turnoff | in std_logic := ' 0 ' |

| cfg_turnoff_ok | out std_logic := ' 0 ' |

| np_counter | out std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| user_clk | in std_logic := ' 0 ' |

| user_rst | in std_logic := ' 0 ' |

Подробное описание

См. определение в файле axi_basic_top.vhd строка 71

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/source_virtex6/axi_basic_top.vhd

1.7.4

1.7.4