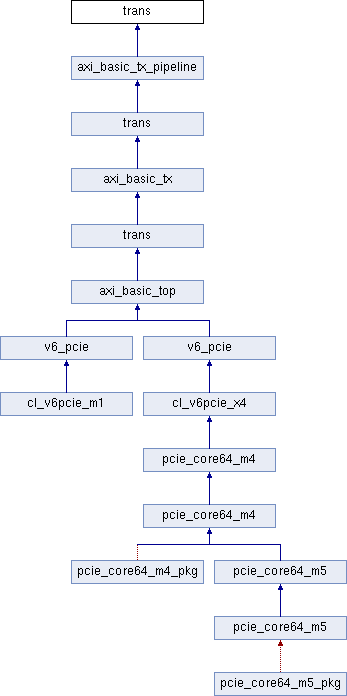

Граф наследования:trans:

Processes | |

| PROCESS_25 | ( USER_CLK ) |

| PROCESS_26 | ( USER_CLK ) |

| PROCESS_27 | ( USER_CLK ) |

| PROCESS_28 | ( USER_CLK ) |

| PROCESS_29 | ( USER_CLK ) |

| PROCESS_30 | ( USER_CLK ) |

| PROCESS_31 | ( USER_CLK ) |

| PROCESS_32 | ( USER_CLK ) |

| PROCESS_33 | ( USER_CLK ) |

| PROCESS_34 | ( USER_CLK ) |

Signals | |

| reg_tdata | STD_LOGIC_VECTOR ( C_DATA_WIDTH- 1 DOWNTO 0 ) |

| tdata_prev | STD_LOGIC_VECTOR ( C_DATA_WIDTH- 1 DOWNTO 0 ) |

| tstrb_prev | STD_LOGIC_VECTOR ( C_STRB_WIDTH- 1 DOWNTO 0 ) |

| tvalid_prev | STD_LOGIC |

| tlast_prev | STD_LOGIC |

| reg_tdst_rdy | STD_LOGIC |

| data_hold | STD_LOGIC |

| data_prev | STD_LOGIC |

| tuser_prev | STD_LOGIC_VECTOR ( 3 DOWNTO 0 ) |

| reg_tvalid | STD_LOGIC |

| reg_tstrb | STD_LOGIC_VECTOR ( C_STRB_WIDTH- 1 DOWNTO 0 ) |

| reg_tuser | STD_LOGIC_VECTOR ( 3 DOWNTO 0 ) |

| reg_tlast | STD_LOGIC |

| reg_tready | STD_LOGIC |

| trn_in_packet | STD_LOGIC |

| axi_in_packet | STD_LOGIC |

| flush_axi | STD_LOGIC |

| disable_trn | STD_LOGIC |

| reg_disable_trn | STD_LOGIC |

| axi_beat_live | STD_LOGIC |

| axi_end_packet | STD_LOGIC |

| reg_tsrc_rdy | STD_LOGIC |

| s_axis_tx_tready_xhdl0 | STD_LOGIC |

| trn_tsof_xhdl2 | STD_LOGIC |

| trn_teof_xhdl1 | STD_LOGIC |

| trn_tsrc_rdy_xhdl3 | STD_LOGIC |

| axi_DW_1 | STD_LOGIC |

| axi_DW_2 | STD_LOGIC |

| axi_DW_3 | STD_LOGIC |

Подробное описание

См. определение в файле axi_basic_tx_pipeline.vhd строка 124

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/source_virtex6/axi_basic_tx_pipeline.vhd

1.7.4

1.7.4