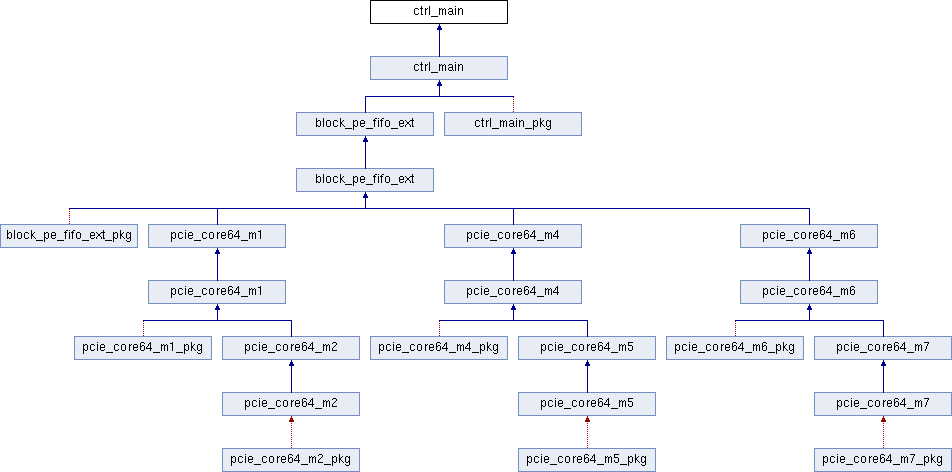

Граф наследования:ctrl_main:

Processes | |

| pr_dma_flag_start | ( clk ) |

| pr_chn | ( clk ) |

| pr_init | ( clk ) |

| pr_state | ( clk ) |

| pr_dma_eot | ( clk ) |

| pr_dma0_wait_eot | ( clk ) |

| pr_dma_start | ( clk ) |

Types | |

| st_type | ( s0 , s01 , s1 , s2 , s3 , s4 , st0 , st1 , st20 , st2 , sc0 , sc1 , sc2 , sc3 , sc4 , sr0 , sr1 , sr2 , sr3 , sr4 , sr5 , sr6 ) |

| stw_type | ( s0 , s01 , s02 , s03 , s1 , s2 , s3 , s4 , s5 , s6 , s7 ) |

Signals | |

| dma0_eot | std_logic |

| dma1_eot | std_logic |

| dma0_sg_eot | std_logic |

| dma1_sg_eot | std_logic |

| dma_eot_set | std_logic |

| dma_sg_eot_set | std_logic |

| ra | std_logic_vector ( 7 downto 0 ) |

| dma_chni | std_logic := ' 0 ' |

| ram_a_adr | std_logic_vector ( 8 downto 0 ) |

| ram_a_out | std_logic_vector ( 31 downto 0 ) |

| rstp | std_logic |

| dma_chn_change_en | std_logic |

| dma0_ctrl_z | std_logic |

| dma1_ctrl_z | std_logic |

| dma0_flag_start | std_logic |

| dma1_flag_start | std_logic |

| dma_flag_start | std_logic |

| dma_flag_start_clr | std_logic |

| dma_transfer_start | std_logic |

| dma_chn_change | std_logic |

| dma0_start | std_logic |

| dma1_start | std_logic |

| ram_adr_l | std_logic_vector ( 2 downto 0 ) |

| dma_start | std_logic |

| dma0_wait_eot | std_logic |

| dma1_wait_eot | std_logic |

| dma0_wait_eot2 | std_logic |

| dma1_wait_eot2 | std_logic |

| stp | st_type |

| ram_sel | std_logic_vector ( 2 downto 0 ) |

| stw | stw_type |

| init_compelte | std_logic |

| dma_rotate | std_logic |

| dma0_block | std_logic |

| dma1_block | std_logic |

| dma0_block_in | std_logic |

| dma1_block_in | std_logic |

| dma0_block_z | std_logic |

| dma1_block_z | std_logic |

Component Instantiations | |

| xb0 | srl16 |

| xb1 | srl16 |

Подробное описание

См. определение в файле ctrl_main.vhd строка 146

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/pcie_fifo_ext/ctrl_main.vhd

1.7.4

1.7.4