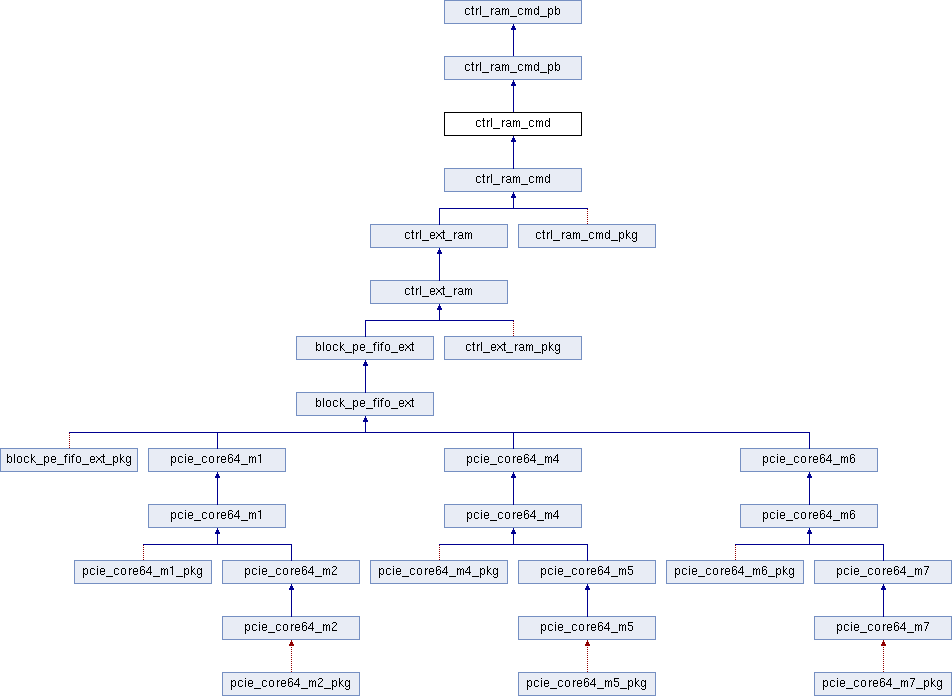

Граф наследования:ctrl_ram_cmd:

Processes | |

| pr_current_block0 | ( clk ) |

| pr_current_block1 | ( clk ) |

| PROCESS_0 | ( clk ) |

| pr0_transfer_rdy | ( clk ) |

| pr1_transfer_rdy | ( clk ) |

| pr_state | ( aclk ) |

| pr_pf_ram_rd | ( aclk ) |

| pr_dsp | ( clk ) |

| pr_ch0_adr_hi | ( clk ) |

| pr_ch1_adr_hi | ( clk ) |

Types | |

| stp_type | ( s0 , s1 , s2 , s3 ) |

Signals | |

| pb_current_block | std_logic_vector ( 1 downto 0 ) |

| flag_data | std_logic_vector ( 3 downto 0 ) |

| cb | std_logic |

| pb_flag_set | std_logic_vector ( 3 downto 0 ) |

| pb_flag_clr | std_logic_vector ( 3 downto 0 ) |

| pf_flag_set | std_logic_vector ( 3 downto 0 ) |

| pf_flag_clr | std_logic_vector ( 3 downto 0 ) |

| pb_fclr | std_logic |

| pb_fset | std_logic |

| reg_write_E0_z | std_logic |

| reg_write_E0_z1 | std_logic |

| pf_chn | std_logic |

| pf0_act | std_logic |

| pf0_rdy | std_logic |

| pf1_act | std_logic |

| pf1_rdy | std_logic |

| stp | stp_type |

| rst_p | std_logic |

| rst_p0 | std_logic |

| pf0_cb | std_logic |

| pf0_dma_wr_rdy | std_logic |

| pf0_dma_rd_rdy | std_logic |

| pf1_cb | std_logic |

| pf1_dma_wr_rdy | std_logic |

| pf1_dma_rd_rdy | std_logic |

| ram0_transfer_rdy | std_logic |

| ram1_transfer_rdy | std_logic |

| port_a | std_logic_vector ( 17 downto 0 ) |

| port_b | std_logic_vector ( 17 downto 0 ) |

| port_c | std_logic_vector ( 47 downto 0 ) |

| port_p | std_logic_vector ( 47 downto 0 ) |

| opmode | std_logic_vector ( 6 downto 0 ) |

| carry | std_logic |

| cnt_rstp | std_logic |

| ch0_adr_hi | std_logic_vector ( 1 downto 0 ) |

| ch1_adr_hi | std_logic_vector ( 1 downto 0 ) |

| ch0_next_block | std_logic |

| ch1_next_block | std_logic |

| ch0_adr_hi_wr | std_logic |

| ch1_adr_hi_wr | std_logic |

| pf_ram_rd | std_logic |

| pf_dma_wr_rdy | std_logic |

| pf_dma_rd_rdy | std_logic |

Component Instantiations | |

| cmd0 | ctrl_ram_cmd_pb <Entity ctrl_ram_cmd_pb> |

| cmd1 | ctrl_ram_cmd_pb <Entity ctrl_ram_cmd_pb> |

| dsp | DSP48 |

Подробное описание

См. определение в файле ctrl_ram_cmd.vhd строка 120

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/pcie_fifo_ext/ctrl_ram_cmd.vhd

1.7.4

1.7.4