контроллер PCI-Express. Подробнее...

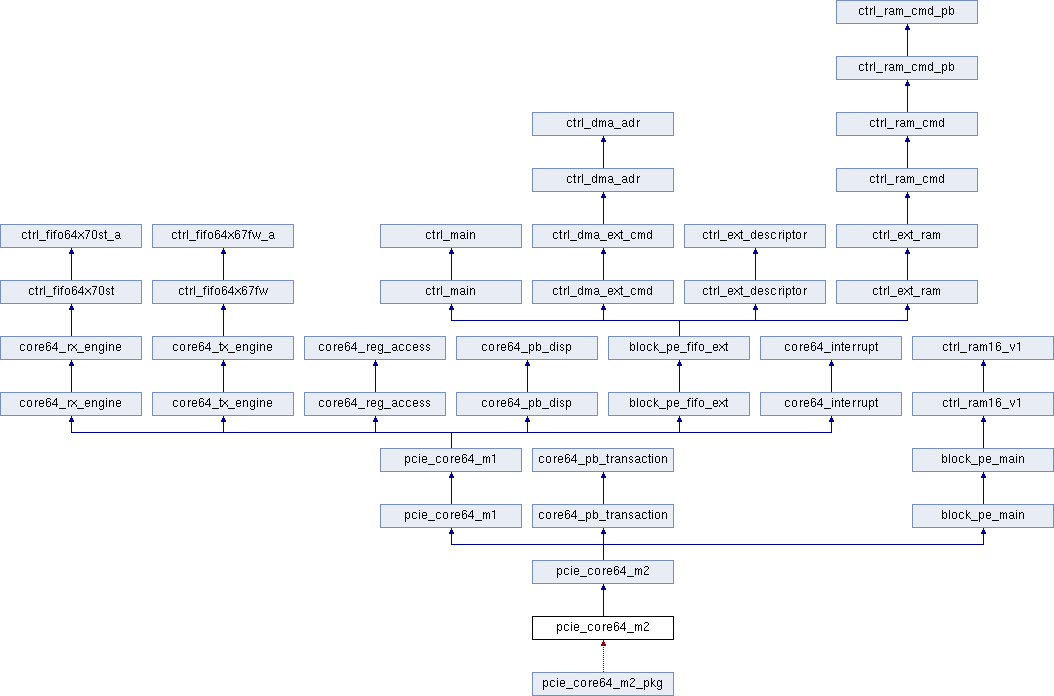

Граф наследования:pcie_core64_m2:

Architectures | |

| pcie_core64_m2 | Architecture |

Libraries | |

| ieee | |

Packages | |

| std_logic_1164 | |

| core64_type_pkg | Package <core64_type_pkg> |

| pcie_core64_m1_pkg | Package <pcie_core64_m1_pkg> |

| core64_pb_transaction_pkg | Package <core64_pb_transaction_pkg> |

| block_pe_main_pkg | Package <block_pe_main_pkg> |

Generics | |

| Device_ID | in std_logic_vector ( 15 downto 0 ) := x " 0000 " |

| Revision | in std_logic_vector ( 15 downto 0 ) := x " 0000 " |

| PLD_VER | in std_logic_vector ( 15 downto 0 ) := x " 0000 " |

| is_simulation | integer := 0 |

| 0 - синтез, 1 - моделирование | |

Ports | |

| txp | out std_logic_vector ( 7 downto 0 ) |

| txn | out std_logic_vector ( 7 downto 0 ) |

| rxp | in std_logic_vector ( 7 downto 0 ) |

| rxn | in std_logic_vector ( 7 downto 0 ) |

| mgt250 | in std_logic |

| perst | in std_logic |

| px | out std_logic_vector ( 7 downto 0 ) |

| контрольные точки | |

| pcie_lstatus | out std_logic_vector ( 15 downto 0 ) |

| pcie_link_up | out std_logic |

| clk250_out | out std_logic |

| тактовая частота 250 MHz. | |

| reset_out | out std_logic |

| 0 - сброс | |

| dcm_rstp | out std_logic |

| 1 - сброс DCM 266 МГц | |

| clk | in std_logic |

| тактовая частота локальной шины - 266 МГц | |

| clk_lock | in std_logic |

| 1 - захват частота | |

| lc_adr | out std_logic_vector ( 31 downto 0 ) |

| шина адреса | |

| lc_host_data | out std_logic_vector ( 63 downto 0 ) |

| шина данных - выход | |

| lc_data | in std_logic_vector ( 63 downto 0 ) |

| шина данных - вход | |

| lc_wr | out std_logic |

| 1 - запись | |

| lc_rd | out std_logic |

| 1 - чтение, данные должны быть на четвёртый такт после rd | |

| lc_dma_req | in std_logic_vector ( 1 downto 0 ) |

| 1 - запрос DMA | |

| lc_irq | in std_logic |

| 1 - запрос прерывания | |

Подробное описание

контроллер PCI-Express.

См. определение в файле pcie_core64_m2.vhd строка 86

Объявления и описания членов класса находятся в файле:

- pcie_src/components/pcie_core/pcie_core64_m2.vhd

1.7.4

1.7.4