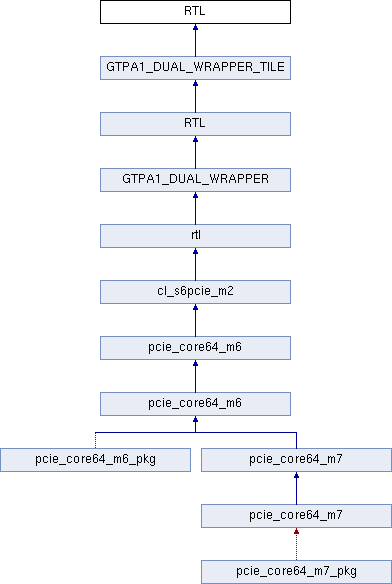

Граф наследования:RTL:

Signals | |

| tied_to_ground_i | std_logic |

| tied_to_ground_vec_i | std_logic_vector ( 63 downto 0 ) |

| tied_to_vcc_i | std_logic |

| tied_to_vcc_vec_i | std_logic_vector ( 63 downto 0 ) |

| rxdata0_i | std_logic_vector ( 31 downto 0 ) |

| rxchariscomma0_float_i | std_logic_vector ( 1 downto 0 ) |

| rxcharisk0_float_i | std_logic_vector ( 1 downto 0 ) |

| rxdisperr0_float_i | std_logic_vector ( 1 downto 0 ) |

| rxnotintable0_float_i | std_logic_vector ( 1 downto 0 ) |

| rxrundisp0_float_i | std_logic_vector ( 1 downto 0 ) |

| txdata0_i | std_logic_vector ( 31 downto 0 ) |

| txkerr0_float_i | std_logic_vector ( 1 downto 0 ) |

| txrundisp0_float_i | std_logic_vector ( 1 downto 0 ) |

| rxdata1_i | std_logic_vector ( 31 downto 0 ) |

| rxchariscomma1_float_i | std_logic_vector ( 1 downto 0 ) |

| rxcharisk1_float_i | std_logic_vector ( 1 downto 0 ) |

| rxdisperr1_float_i | std_logic_vector ( 1 downto 0 ) |

| rxnotintable1_float_i | std_logic_vector ( 1 downto 0 ) |

| rxrundisp1_float_i | std_logic_vector ( 1 downto 0 ) |

| txdata1_i | std_logic_vector ( 31 downto 0 ) |

| txkerr1_float_i | std_logic_vector ( 1 downto 0 ) |

| txrundisp1_float_i | std_logic_vector ( 1 downto 0 ) |

Component Instantiations | |

| gtpa1_dual_i | GTPA1_DUAL |

Подробное описание

См. определение в файле gtpa1_dual_wrapper_tile.vhd строка 182

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/source_s6/gtpa1_dual_wrapper_tile.vhd

1.7.4

1.7.4