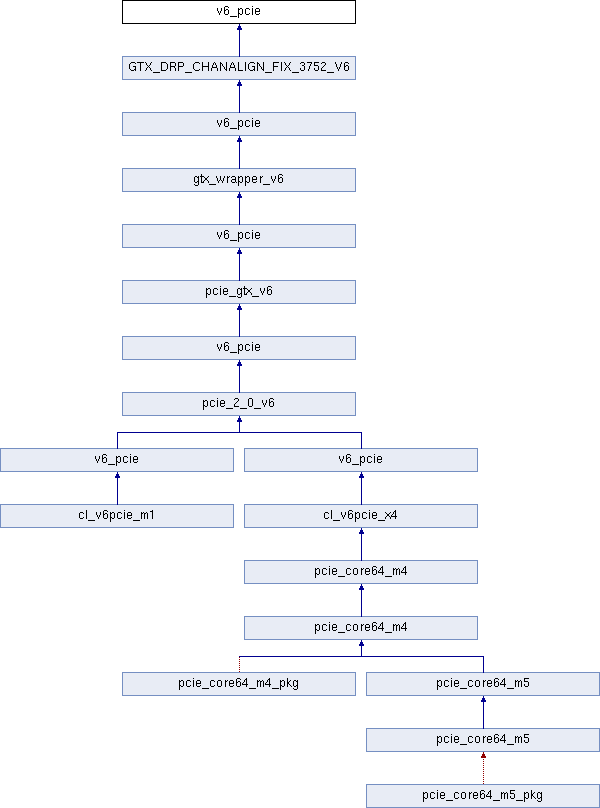

Граф наследования:v6_pcie:

Processes | |

| PROCESS_49 | ( drp_clk ) |

| PROCESS_50 | ( drpstate_v6pcie , daddr_v6pcie , drdy , write_ts1_gated , write_fts_gated ) |

Constants | |

| TCQ | integer := 1 |

| DRP_IDLE_FTS | std_logic_vector ( 3 downto 0 ) := " 0001 " |

| DRP_IDLE_TS1 | std_logic_vector ( 3 downto 0 ) := " 0010 " |

| DRP_RESET | std_logic_vector ( 3 downto 0 ) := " 0011 " |

| DRP_WRITE_FTS | std_logic_vector ( 3 downto 0 ) := " 0110 " |

| DRP_WRITE_DONE_FTS | std_logic_vector ( 3 downto 0 ) := " 0111 " |

| DRP_WRITE_TS1 | std_logic_vector ( 3 downto 0 ) := " 1000 " |

| DRP_WRITE_DONE_TS1 | std_logic_vector ( 3 downto 0 ) := " 1001 " |

| DRP_COM | std_logic_vector ( 9 downto 0 ) := " 0110111100 " |

| DRP_FTS | std_logic_vector ( 9 downto 0 ) := " 0100111100 " |

| DRP_TS1 | std_logic_vector ( 9 downto 0 ) := " 0001001010 " |

Signals | |

| next_daddr | std_logic_vector ( 7 downto 0 ) |

| next_drpstate | std_logic_vector ( 3 downto 0 ) |

| write_ts1_gated | std_logic |

| write_fts_gated | std_logic |

| daddr_v6pcie | std_logic_vector ( 7 downto 0 ) |

| drpstate_v6pcie | std_logic_vector ( 3 downto 0 ) |

Подробное описание

См. определение в файле gtx_drp_chanalign_fix_3752_v6.vhd строка 84

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/source_virtex6/gtx_drp_chanalign_fix_3752_v6.vhd

1.7.4

1.7.4