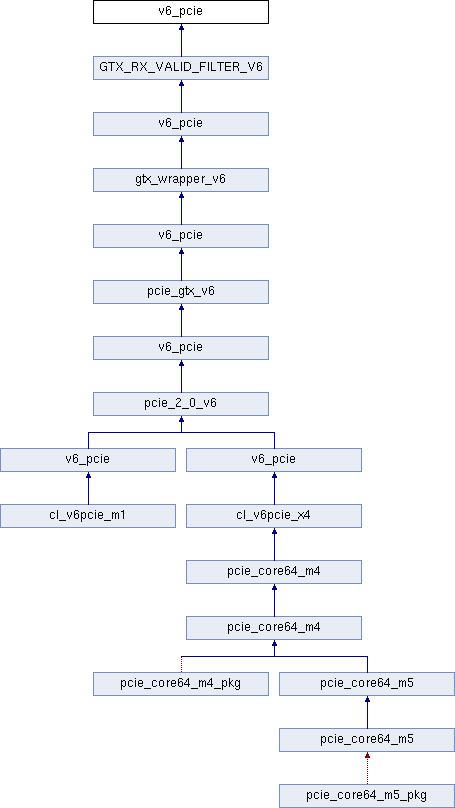

Граф наследования:v6_pcie:

Functions | |

| std_logic_vector | to_stdlogicvector ( val_in: in integer , length: in integer ) |

| std_logic | to_stdlogic ( in_val: in boolean ) |

Processes | |

| PROCESS_51 | ( USER_CLK ) |

| PROCESS_52 | ( USER_CLK ) |

| PROCESS_53 | ( USER_CLK ) |

| PROCESS_54 | ( USER_CLK ) |

| PROCESS_55 | ( USER_CLK ) |

Constants | |

| TCQ | integer := 1 |

| EIOS_DET_IDL | std_logic_vector ( 4 downto 0 ) := " 00001 " |

| EIOS_DET_NO_STR0 | std_logic_vector ( 4 downto 0 ) := " 00010 " |

| EIOS_DET_STR0 | std_logic_vector ( 4 downto 0 ) := " 00100 " |

| EIOS_DET_STR1 | std_logic_vector ( 4 downto 0 ) := " 01000 " |

| EIOS_DET_DONE | std_logic_vector ( 4 downto 0 ) := " 10000 " |

| EIOS_COM | std_logic_vector ( 7 downto 0 ) := " 10111100 " |

| EIOS_IDL | std_logic_vector ( 7 downto 0 ) := " 01111100 " |

| FTSOS_COM | std_logic_vector ( 7 downto 0 ) := " 10111100 " |

| FTSOS_FTS | std_logic_vector ( 7 downto 0 ) := " 00111100 " |

| USER_RXVLD_IDL | std_logic_vector ( 3 downto 0 ) := " 0001 " |

| USER_RXVLD_EI | std_logic_vector ( 3 downto 0 ) := " 0010 " |

| USER_RXVLD_EI_DB0 | std_logic_vector ( 3 downto 0 ) := " 0100 " |

| USER_RXVLD_EI_DB1 | std_logic_vector ( 3 downto 0 ) := " 1000 " |

| TS1_FILTER_IDLE | std_logic_vector ( 2 downto 0 ) := " 001 " |

| TS1_FILTER_WAITVALID | std_logic_vector ( 2 downto 0 ) := " 010 " |

| TS1_FILTER_DB | std_logic_vector ( 2 downto 0 ) := " 100 " |

Signals | |

| reg_state_eios_det | std_logic_vector ( 4 downto 0 ) |

| state_eios_det | std_logic_vector ( 4 downto 0 ) |

| reg_eios_detected | std_logic |

| eios_detected | std_logic |

| reg_symbol_after_eios | std_logic |

| symbol_after_eios | std_logic |

| reg_state_rxvld_ei | std_logic_vector ( 3 downto 0 ) |

| state_rxvld_ei | std_logic_vector ( 3 downto 0 ) |

| reg_rxvld_count | std_logic_vector ( 4 downto 0 ) |

| rxvld_count | std_logic_vector ( 4 downto 0 ) |

| reg_rxvld_fallback | std_logic_vector ( 3 downto 0 ) |

| rxvld_fallback | std_logic_vector ( 3 downto 0 ) |

| gt_rxcharisk_q | std_logic_vector ( 1 downto 0 ) |

| gt_rxdata_q | std_logic_vector ( 15 downto 0 ) |

| gt_rxvalid_q | std_logic |

| gt_rxelecidle_q | std_logic |

| gt_rxelecidle_qq | std_logic |

| gt_rx_status_q | std_logic_vector ( 2 downto 0 ) |

| gt_rx_phy_status_q | std_logic |

| gt_rx_is_skp0_q | std_logic |

| gt_rx_is_skp1_q | std_logic |

| ts1_state | std_logic_vector ( 2 downto 0 ) |

| next_ts1_state | std_logic_vector ( 2 downto 0 ) |

| ts1_resetcount | std_logic |

| ts1_count | std_logic_vector ( 8 downto 0 ) |

| ts1_filter_done | std_logic |

| next_ts1_filter_done | std_logic |

| awake_in_progress_q | std_logic := ' 0 ' |

| awake_in_progress | std_logic := ' 0 ' |

| awake_see_com_q | std_logic := ' 0 ' |

| awake_com_count_q | std_logic_vector ( 3 downto 0 ) := " 0000 " |

| awake_com_count | std_logic_vector ( 3 downto 0 ) := " 0000 " |

| awake_com_count_inced | std_logic_vector ( 3 downto 0 ) := " 0000 " |

| awake_see_com_0 | std_logic |

| awake_see_com_1 | std_logic |

| awake_see_com | std_logic |

| awake_done | std_logic |

| awake_start | std_logic |

| rst_l | std_logic |

| USER_RXVALID_v6pcie1 | std_logic |

| USER_RXELECIDLE_v6pcie0 | std_logic |

Component Instantiations | |

| rx_elec_idle_delay | SRL16E |

Подробное описание

См. определение в файле gtx_rx_valid_filter_v6.vhd строка 87

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/source_virtex6/gtx_rx_valid_filter_v6.vhd

1.7.4

1.7.4