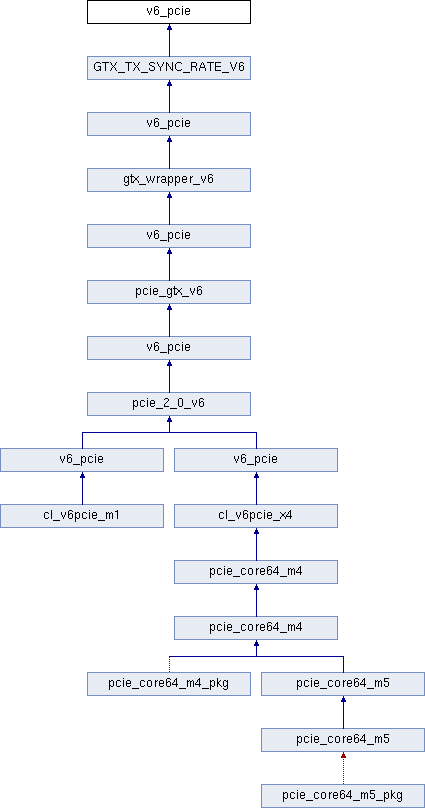

Граф наследования:v6_pcie:

Functions | |

| std_logic | to_stdlogic ( in_val: in boolean ) |

| integer | s_idx ( constant C_SIMULATION: in integer ) |

| integer | pma_idx ( constant C_SIMULATION: in integer ) |

Processes | |

| PROCESS_56 | ( USER_CLK ) |

| PROCESS_57 | ( state , GT_PHYSTATUS , waitcounter , waitcounter2 , waitcounter2_check , ratedone_pulse_i , gt_phystatus_q , RESETDONE ) |

| PROCESS_58 | ( USER_CLK ) |

Constants | |

| TCQ | integer := 1 |

| IDLE | std_logic_vector ( 24 downto 0 ) := " 0000000000000000000000001 " |

| PHASEALIGN | std_logic_vector ( 24 downto 0 ) := " 0000000000000000000000010 " |

| RATECHANGE_DIVRESET | std_logic_vector ( 24 downto 0 ) := " 0000000000000000000000100 " |

| RATECHANGE_DIVRESET_POST | std_logic_vector ( 24 downto 0 ) := " 0000000000000000000001000 " |

| RATECHANGE_ENPMADISABLE | std_logic_vector ( 24 downto 0 ) := " 0000000000000000000010000 " |

| RATECHANGE_ENPMADISABLE_POST | std_logic_vector ( 24 downto 0 ) := " 0000000000000000000100000 " |

| RATECHANGE_PMARESET | std_logic_vector ( 24 downto 0 ) := " 0000000000000000001000000 " |

| RATECHANGE_IDLE | std_logic_vector ( 24 downto 0 ) := " 0000000000000000010000000 " |

| RATECHANGE_PCSRESET | std_logic_vector ( 24 downto 0 ) := " 0000000000000000100000000 " |

| RATECHANGE_PCSRESET_POST | std_logic_vector ( 24 downto 0 ) := " 0000000000000001000000000 " |

| RATECHANGE_ASSERTPHY | std_logic_vector ( 24 downto 0 ) := " 0000000000000010000000000 " |

| RESET_STATE | std_logic_vector ( 24 downto 0 ) := " 0000000000000100000000000 " |

| WAIT_PHYSTATUS | std_logic_vector ( 24 downto 0 ) := " 0000000000010000000000000 " |

| RATECHANGE_PMARESET_POST | std_logic_vector ( 24 downto 0 ) := " 0000000000100000000000000 " |

| RATECHANGE_DISABLEPHASE | std_logic_vector ( 24 downto 0 ) := " 0000000001000000000000000 " |

| DELAYALIGNRST | std_logic_vector ( 24 downto 0 ) := " 0000000010000000000000000 " |

| SETENPMAPHASEALIGN | std_logic_vector ( 24 downto 0 ) := " 0000000100000000000000000 " |

| TXALIGNDISABLEDEASSERT | std_logic_vector ( 24 downto 0 ) := " 0000001000000000000000000 " |

| RATECHANGE_TXDLYALIGNDISABLE | std_logic_vector ( 24 downto 0 ) := " 0000010000000000000000000 " |

| GTXTEST_PULSE_1 | std_logic_vector ( 24 downto 0 ) := " 0000100000000000000000000 " |

| RATECHANGE_DISABLE_TXALIGNDISABLE | std_logic_vector ( 24 downto 0 ) := " 0001000000000000000000000 " |

| BEFORE_GTXTEST_PULSE1_1024CLKS | std_logic_vector ( 24 downto 0 ) := " 0010000000000000000000000 " |

| BETWEEN_GTXTEST_PULSES | std_logic_vector ( 24 downto 0 ) := " 0100000000000000000000000 " |

| GTXTEST_PULSE_2 | std_logic_vector ( 24 downto 0 ) := " 1000000000000000000000000 " |

| SYNC_IDX | integer := s_idx ( C_SIMULATION ) |

| PMARESET_IDX | integer := pma_idx ( C_SIMULATION ) |

Signals | |

| ENPMAPHASEALIGN_c | std_logic |

| PMASETPHASE_c | std_logic |

| SYNC_DONE_c | std_logic |

| OUT_DIV_RESET_c | std_logic |

| PCS_RESET_c | std_logic |

| USER_PHYSTATUS_c | std_logic |

| DELAYALIGNRESET_c | std_logic |

| TXALIGNDISABLE_c | std_logic |

| state | std_logic_vector ( 24 downto 0 ) |

| nextstate | std_logic_vector ( 24 downto 0 ) |

| wait_amt | std_logic_vector ( 15 downto 0 ) |

| wait_c | std_logic_vector ( 15 downto 0 ) |

| waitcounter | std_logic_vector ( 7 downto 0 ) |

| nextwaitcounter | std_logic_vector ( 7 downto 0 ) |

| waitcounter2 | std_logic_vector ( 7 downto 0 ) |

| waitcounter2_check | std_logic_vector ( 7 downto 0 ) |

| nextwaitcounter2 | std_logic_vector ( 7 downto 0 ) |

| ratedone_r | std_logic |

| ratedone_r2 | std_logic |

| ratedone_pulse_i | std_logic |

| gt_phystatus_q | std_logic |

| state_v6pcie0 | std_logic_vector ( 4 downto 0 ) |

Подробное описание

См. определение в файле gtx_tx_sync_rate_v6.vhd строка 87

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/source_virtex6/gtx_tx_sync_rate_v6.vhd

1.7.4

1.7.4