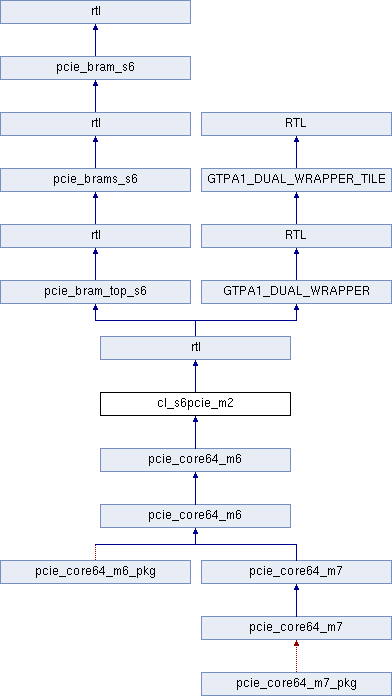

Граф наследования:cl_s6pcie_m2:

Architectures | |

| rtl | Architecture |

Libraries | |

| ieee | |

| unisim | |

| secureip | |

Packages | |

| std_logic_1164 | |

| std_logic_arith | |

| std_logic_unsigned | |

| numeric_bit | |

| vcomponents | |

| vpkg | |

| all | |

Generics | |

| TL_TX_RAM_RADDR_LATENCY | integer := 0 |

| TL_TX_RAM_RDATA_LATENCY | integer := 2 |

| TL_RX_RAM_RADDR_LATENCY | integer := 0 |

| TL_RX_RAM_RDATA_LATENCY | integer := 2 |

| TL_RX_RAM_WRITE_LATENCY | integer := 0 |

| VC0_TX_LASTPACKET | integer := 28 |

| VC0_RX_RAM_LIMIT | bit_vector := x " 7ff " |

| VC0_TOTAL_CREDITS_PH | integer := 32 |

| VC0_TOTAL_CREDITS_PD | integer := 211 |

| VC0_TOTAL_CREDITS_NPH | integer := 8 |

| VC0_TOTAL_CREDITS_CH | integer := 40 |

| VC0_TOTAL_CREDITS_CD | integer := 211 |

| VC0_CPL_INFINITE | boolean := true |

| BAR0 | bit_vector := x " ffe00000 " |

| BAR1 | bit_vector := x " ffe00000 " |

| BAR2 | bit_vector := x " 00000000 " |

| BAR3 | bit_vector := x " 00000000 " |

| BAR4 | bit_vector := x " 00000000 " |

| BAR5 | bit_vector := x " 00000000 " |

| EXPANSION_ROM | bit_vector := " 0000000000000000000000 " |

| DISABLE_BAR_FILTERING | boolean := false |

| DISABLE_ID_CHECK | boolean := false |

| TL_TFC_DISABLE | boolean := false |

| TL_TX_CHECKS_DISABLE | boolean := false |

| USR_CFG | boolean := false |

| USR_EXT_CFG | boolean := false |

| DEV_CAP_MAX_PAYLOAD_SUPPORTED | integer := 1 |

| CLASS_CODE | bit_vector := x " ffffff " |

| CARDBUS_CIS_POINTER | bit_vector := x " 00000000 " |

| PCIE_CAP_CAPABILITY_VERSION | bit_vector := x " 1 " |

| PCIE_CAP_DEVICE_PORT_TYPE | bit_vector := x " 0 " |

| PCIE_CAP_SLOT_IMPLEMENTED | boolean := false |

| PCIE_CAP_INT_MSG_NUM | bit_vector := " 00000 " |

| DEV_CAP_PHANTOM_FUNCTIONS_SUPPORT | integer := 0 |

| DEV_CAP_EXT_TAG_SUPPORTED | boolean := false |

| DEV_CAP_ENDPOINT_L0S_LATENCY | integer := 7 |

| DEV_CAP_ENDPOINT_L1_LATENCY | integer := 7 |

| SLOT_CAP_ATT_BUTTON_PRESENT | boolean := false |

| SLOT_CAP_ATT_INDICATOR_PRESENT | boolean := false |

| SLOT_CAP_POWER_INDICATOR_PRESENT | boolean := false |

| DEV_CAP_ROLE_BASED_ERROR | boolean := true |

| LINK_CAP_ASPM_SUPPORT | integer := 1 |

| LINK_CAP_L0S_EXIT_LATENCY | integer := 7 |

| LINK_CAP_L1_EXIT_LATENCY | integer := 7 |

| LL_ACK_TIMEOUT | bit_vector := x " 0000 " |

| LL_ACK_TIMEOUT_EN | boolean := false |

| LL_REPLAY_TIMEOUT | bit_vector := x " 0000 " |

| LL_REPLAY_TIMEOUT_EN | boolean := false |

| MSI_CAP_MULTIMSGCAP | integer := 0 |

| MSI_CAP_MULTIMSG_EXTENSION | integer := 0 |

| LINK_STATUS_SLOT_CLOCK_CONFIG | boolean := true |

| PLM_AUTO_CONFIG | boolean := false |

| FAST_TRAIN | boolean := false |

| ENABLE_RX_TD_ECRC_TRIM | boolean := true |

| DISABLE_SCRAMBLING | boolean := false |

| PM_CAP_VERSION | integer := 3 |

| PM_CAP_PME_CLOCK | boolean := false |

| PM_CAP_DSI | boolean := false |

| PM_CAP_AUXCURRENT | integer := 0 |

| PM_CAP_D1SUPPORT | boolean := true |

| PM_CAP_D2SUPPORT | boolean := true |

| PM_CAP_PMESUPPORT | bit_vector := x " 0f " |

| PM_DATA0 | bit_vector := x " 00 " |

| PM_DATA_SCALE0 | bit_vector := x " 0 " |

| PM_DATA1 | bit_vector := x " 00 " |

| PM_DATA_SCALE1 | bit_vector := x " 0 " |

| PM_DATA2 | bit_vector := x " 00 " |

| PM_DATA_SCALE2 | bit_vector := x " 0 " |

| PM_DATA3 | bit_vector := x " 00 " |

| PM_DATA_SCALE3 | bit_vector := x " 0 " |

| PM_DATA4 | bit_vector := x " 00 " |

| PM_DATA_SCALE4 | bit_vector := x " 0 " |

| PM_DATA5 | bit_vector := x " 00 " |

| PM_DATA_SCALE5 | bit_vector := x " 0 " |

| PM_DATA6 | bit_vector := x " 00 " |

| PM_DATA_SCALE6 | bit_vector := x " 0 " |

| PM_DATA7 | bit_vector := x " 00 " |

| PM_DATA_SCALE7 | bit_vector := x " 0 " |

| PCIE_GENERIC | bit_vector := " 000010101111 " |

| GTP_SEL | integer := 0 |

| CFG_VEN_ID | std_logic_vector ( 15 downto 0 ) := x " 4953 " |

| CFG_DEV_ID | std_logic_vector ( 15 downto 0 ) := x " 5507 " |

| CFG_REV_ID | std_logic_vector ( 7 downto 0 ) := x " 10 " |

| CFG_SUBSYS_VEN_ID | std_logic_vector ( 15 downto 0 ) := x " 4953 " |

| CFG_SUBSYS_ID | std_logic_vector ( 15 downto 0 ) := x " 0008 " |

| REF_CLK_FREQ | integer := 1 |

Ports | |

| pci_exp_txp | out std_logic |

| pci_exp_txn | out std_logic |

| pci_exp_rxp | in std_logic |

| pci_exp_rxn | in std_logic |

| trn_lnk_up_n | out std_logic |

| trn_td | in std_logic_vector ( 31 downto 0 ) |

| trn_tsof_n | in std_logic |

| trn_teof_n | in std_logic |

| trn_tsrc_rdy_n | in std_logic |

| trn_tdst_rdy_n | out std_logic |

| trn_terr_drop_n | out std_logic |

| trn_tsrc_dsc_n | in std_logic |

| trn_terrfwd_n | in std_logic |

| trn_tbuf_av | out std_logic_vector ( 5 downto 0 ) |

| trn_tstr_n | in std_logic |

| trn_tcfg_req_n | out std_logic |

| trn_tcfg_gnt_n | in std_logic |

| trn_rd | out std_logic_vector ( 31 downto 0 ) |

| trn_rsof_n | out std_logic |

| trn_reof_n | out std_logic |

| trn_rsrc_rdy_n | out std_logic |

| trn_rsrc_dsc_n | out std_logic |

| trn_rdst_rdy_n | in std_logic |

| trn_rerrfwd_n | out std_logic |

| trn_rnp_ok_n | in std_logic |

| trn_rbar_hit_n | out std_logic_vector ( 6 downto 0 ) |

| trn_fc_sel | in std_logic_vector ( 2 downto 0 ) |

| trn_fc_nph | out std_logic_vector ( 7 downto 0 ) |

| trn_fc_npd | out std_logic_vector ( 11 downto 0 ) |

| trn_fc_ph | out std_logic_vector ( 7 downto 0 ) |

| trn_fc_pd | out std_logic_vector ( 11 downto 0 ) |

| trn_fc_cplh | out std_logic_vector ( 7 downto 0 ) |

| trn_fc_cpld | out std_logic_vector ( 11 downto 0 ) |

| cfg_do | out std_logic_vector ( 31 downto 0 ) |

| cfg_rd_wr_done_n | out std_logic |

| cfg_dwaddr | in std_logic_vector ( 9 downto 0 ) |

| cfg_rd_en_n | in std_logic |

| cfg_err_ur_n | in std_logic |

| cfg_err_cor_n | in std_logic |

| cfg_err_ecrc_n | in std_logic |

| cfg_err_cpl_timeout_n | in std_logic |

| cfg_err_cpl_abort_n | in std_logic |

| cfg_err_posted_n | in std_logic |

| cfg_err_locked_n | in std_logic |

| cfg_err_tlp_cpl_header | in std_logic_vector ( 47 downto 0 ) |

| cfg_err_cpl_rdy_n | out std_logic |

| cfg_interrupt_n | in std_logic |

| cfg_interrupt_rdy_n | out std_logic |

| cfg_interrupt_assert_n | in std_logic |

| cfg_interrupt_do | out std_logic_vector ( 7 downto 0 ) |

| cfg_interrupt_di | in std_logic_vector ( 7 downto 0 ) |

| cfg_interrupt_mmenable | out std_logic_vector ( 2 downto 0 ) |

| cfg_interrupt_msienable | out std_logic |

| cfg_turnoff_ok_n | in std_logic |

| cfg_to_turnoff_n | out std_logic |

| cfg_pm_wake_n | in std_logic |

| cfg_pcie_link_state_n | out std_logic_vector ( 2 downto 0 ) |

| cfg_trn_pending_n | in std_logic |

| cfg_dsn | in std_logic_vector ( 63 downto 0 ) |

| cfg_bus_number | out std_logic_vector ( 7 downto 0 ) |

| cfg_device_number | out std_logic_vector ( 4 downto 0 ) |

| cfg_function_number | out std_logic_vector ( 2 downto 0 ) |

| cfg_status | out std_logic_vector ( 15 downto 0 ) |

| cfg_command | out std_logic_vector ( 15 downto 0 ) |

| cfg_dstatus | out std_logic_vector ( 15 downto 0 ) |

| cfg_dcommand | out std_logic_vector ( 15 downto 0 ) |

| cfg_lstatus | out std_logic_vector ( 15 downto 0 ) |

| cfg_lcommand | out std_logic_vector ( 15 downto 0 ) |

| sys_clk | in std_logic |

| sys_reset_n | in std_logic |

| trn_clk | out std_logic |

| trn_reset_n | out std_logic |

| received_hot_reset | out std_logic |

Подробное описание

См. определение в файле cl_s6pcie_m2.vhd строка 69

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/source_s6/cl_s6pcie_m2.vhd

1.7.4

1.7.4