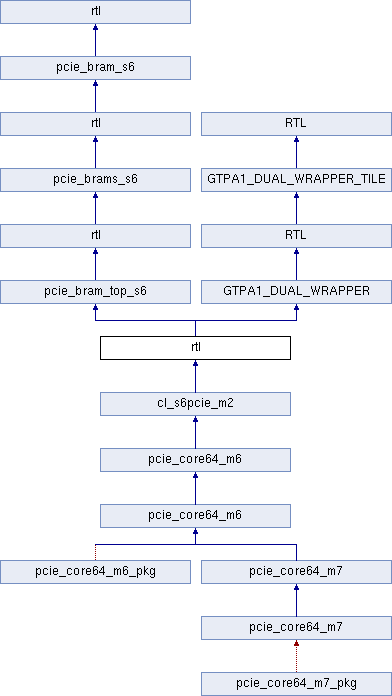

Граф наследования:rtl:

Functions | |

| integer | CALC_CLKFBOUT_MULT ( FREQ_SEL: in integer ) |

| real | CALC_CLKIN_PERIOD ( FREQ_SEL: in integer ) |

| integer | CALC_CLK25_DIVIDER ( FREQ_SEL: in integer ) |

| integer | CALC_PLL_DIVSEL_FB ( FREQ_SEL: in integer ) |

| integer | CALC_PLL_DIVSEL_REF ( FREQ_SEL: in integer ) |

| integer | SIM_INT ( SIMULATION: in boolean ) |

Components | |

| pcie_bram_top_s6 | <Entity pcie_bram_top_s6> |

| GTPA1_DUAL_WRAPPER | <Entity GTPA1_DUAL_WRAPPER> |

Constants | |

| CLKFBOUT_MULT | integer := CALC_CLKFBOUT_MULT ( REF_CLK_FREQ ) |

| CLKIN_PERIOD | real := CALC_CLKIN_PERIOD ( REF_CLK_FREQ ) |

| GT_CLK25_DIVIDER | integer := CALC_CLK25_DIVIDER ( REF_CLK_FREQ ) |

| GT_PLL_DIVSEL_FB | integer := CALC_PLL_DIVSEL_FB ( REF_CLK_FREQ ) |

| GT_PLL_DIVSEL_REF | integer := CALC_PLL_DIVSEL_REF ( REF_CLK_FREQ ) |

Signals | |

| mgt_clk | std_logic |

| mgt_clk_2x | std_logic |

| clock_locked | std_logic |

| gt_refclk_out | std_logic_vector ( 1 downto 0 ) |

| gt_clk_fb_west_out | std_logic |

| pll_rst | std_logic |

| clk_125 | std_logic |

| clk_250 | std_logic |

| clk_62_5 | std_logic |

| gt_refclk_buf | std_logic |

| gt_refclk_fb | std_logic |

| w_cfg_ven_id | std_logic_vector ( 15 downto 0 ) |

| w_cfg_dev_id | std_logic_vector ( 15 downto 0 ) |

| w_cfg_rev_id | std_logic_vector ( 7 downto 0 ) |

| w_cfg_subsys_ven_id | std_logic_vector ( 15 downto 0 ) |

| w_cfg_subsys_id | std_logic_vector ( 15 downto 0 ) |

| cfg_ltssm_state | std_logic_vector ( 4 downto 0 ) |

| cfg_link_control_aspm_control | std_logic_vector ( 1 downto 0 ) |

| cfg_link_control_rcb | std_logic |

| cfg_link_control_common_clock | std_logic |

| cfg_link_control_extended_sync | std_logic |

| cfg_command_interrupt_disable | std_logic |

| cfg_command_serr_en | std_logic |

| cfg_command_bus_master_enable | std_logic |

| cfg_command_mem_enable | std_logic |

| cfg_command_io_enable | std_logic |

| cfg_dev_status_ur_detected | std_logic |

| cfg_dev_status_fatal_err_detected | std_logic |

| cfg_dev_status_nonfatal_err_detected | std_logic |

| cfg_dev_status_corr_err_detected | std_logic |

| cfg_dev_control_max_read_req | std_logic_vector ( 2 downto 0 ) |

| cfg_dev_control_no_snoop_en | std_logic |

| cfg_dev_control_aux_power_en | std_logic |

| cfg_dev_control_phantom_en | std_logic |

| cfg_dev_cntrol_ext_tag_en | std_logic |

| cfg_dev_control_max_payload | std_logic_vector ( 2 downto 0 ) |

| cfg_dev_control_enable_ro | std_logic |

| cfg_dev_control_ext_tag_en | std_logic |

| cfg_dev_control_ur_err_reporting_en | std_logic |

| cfg_dev_control_fatal_err_reporting_en | std_logic |

| cfg_dev_control_non_fatal_reporting_en | std_logic |

| cfg_dev_control_corr_err_reporting_en | std_logic |

| mim_tx_waddr | std_logic_vector ( 11 downto 0 ) |

| mim_tx_raddr | std_logic_vector ( 11 downto 0 ) |

| mim_rx_waddr | std_logic_vector ( 11 downto 0 ) |

| mim_rx_raddr | std_logic_vector ( 11 downto 0 ) |

| mim_tx_wdata | std_logic_vector ( 35 downto 0 ) |

| mim_tx_rdata | std_logic_vector ( 35 downto 0 ) |

| mim_rx_wdata | std_logic_vector ( 34 downto 0 ) |

| mim_rx_rdata_unused | std_logic |

| mim_rx_rdata | std_logic_vector ( 34 downto 0 ) |

| mim_tx_wen | std_logic |

| mim_tx_ren | std_logic |

| mim_rx_wen | std_logic |

| mim_rx_ren | std_logic |

| dbg_bad_dllp_status | std_logic |

| dbg_bad_tlp_lcrc | std_logic |

| dbg_bad_tlp_seq_num | std_logic |

| dbg_bad_tlp_status | std_logic |

| dbg_dl_protocol_status | std_logic |

| dbg_fc_protocol_err_status | std_logic |

| dbg_mlfrmd_length | std_logic |

| dbg_mlfrmd_mps | std_logic |

| dbg_mlfrmd_tcvc | std_logic |

| dbg_mlfrmd_tlp_status | std_logic |

| dbg_mlfrmd_unrec_type | std_logic |

| dbg_poistlpstatus | std_logic |

| dbg_rcvr_overflow_status | std_logic |

| dbg_reg_detected_correctable | std_logic |

| dbg_reg_detected_fatal | std_logic |

| dbg_reg_detected_non_fatal | std_logic |

| dbg_reg_detected_unsupported | std_logic |

| dbg_rply_rollover_status | std_logic |

| dbg_rply_timeout_status | std_logic |

| dbg_ur_no_bar_hit | std_logic |

| dbg_ur_pois_cfg_wr | std_logic |

| dbg_ur_status | std_logic |

| dbg_ur_unsup_msg | std_logic |

| pipe_gt_power_down_a | std_logic_vector ( 1 downto 0 ) |

| pipe_gt_power_down_b | std_logic_vector ( 1 downto 0 ) |

| pipe_gt_reset_done_a | std_logic |

| pipe_gt_reset_done_b | std_logic |

| pipe_gt_tx_elec_idle_a | std_logic |

| pipe_gt_tx_elec_idle_b | std_logic |

| pipe_phy_status_a | std_logic |

| pipe_phy_status_b | std_logic |

| pipe_rx_charisk_a | std_logic_vector ( 1 downto 0 ) |

| pipe_rx_charisk_b | std_logic_vector ( 1 downto 0 ) |

| pipe_rx_data_a | std_logic_vector ( 15 downto 0 ) |

| pipe_rx_data_b | std_logic_vector ( 15 downto 0 ) |

| pipe_rx_enter_elec_idle_a | std_logic |

| pipe_rx_enter_elec_idle_b | std_logic |

| pipe_rx_polarity_a | std_logic |

| pipe_rx_polarity_b | std_logic |

| pipe_rxreset_a | std_logic |

| pipe_rxreset_b | std_logic |

| pipe_rx_status_a | std_logic_vector ( 2 downto 0 ) |

| pipe_rx_status_b | std_logic_vector ( 2 downto 0 ) |

| pipe_tx_char_disp_mode_a | std_logic_vector ( 1 downto 0 ) |

| pipe_tx_char_disp_mode_b | std_logic_vector ( 1 downto 0 ) |

| pipe_tx_char_disp_val_a | std_logic_vector ( 1 downto 0 ) |

| pipe_tx_char_disp_val_b | std_logic_vector ( 1 downto 0 ) |

| pipe_tx_char_is_k_a | std_logic_vector ( 1 downto 0 ) |

| pipe_tx_char_is_k_b | std_logic_vector ( 1 downto 0 ) |

| pipe_tx_data_a | std_logic_vector ( 15 downto 0 ) |

| pipe_tx_data_b | std_logic_vector ( 15 downto 0 ) |

| pipe_tx_rcvr_det_a | std_logic |

| pipe_tx_rcvr_det_b | std_logic |

| rx_char_is_k | std_logic_vector ( 1 downto 0 ) |

| rx_data | std_logic_vector ( 15 downto 0 ) |

| rx_enter_elecidle | std_logic |

| rx_status | std_logic_vector ( 2 downto 0 ) |

| rx_polarity | std_logic |

| tx_char_disp_mode | std_logic_vector ( 1 downto 0 ) |

| tx_char_is_k | std_logic_vector ( 1 downto 0 ) |

| tx_rcvr_det | std_logic |

| tx_data | std_logic_vector ( 15 downto 0 ) |

| phystatus | std_logic |

| gt_reset_done | std_logic |

| gt_rx_valid | std_logic |

| gt_tx_elec_idle | std_logic |

| gt_power_down | std_logic_vector ( 1 downto 0 ) |

| rxreset | std_logic |

| gt_plllkdet_out | std_logic |

| sys_reset | std_logic |

| trn_clk_c | std_logic |

| trn_reset_n_c | std_logic |

| trn_reset | std_logic |

Attributes | |

| CORE_GENERATION_INFO | STRING |

| CORE_GENERATION_INFO | " cl_s6pcie_m2 , s6_pcie_v1_4 , {TL_TX_RAM_RADDR_LATENCY = 0 , TL_TX_RAM_RDATA_LATENCY = 2 , TL_RX_RAM_RADDR_LATENCY = 0 , TL_RX_RAM_RDATA_LATENCY = 2 , TL_RX_RAM_WRITE_LATENCY = 0 , VC0_TX_LASTPACKET = 28 , VC0_RX_RAM_LIMIT = 7FF , VC0_TOTAL_CREDITS_PH = 32 , VC0_TOTAL_CREDITS_PD = 211 , VC0_TOTAL_CREDITS_NPH = 8 , VC0_TOTAL_CREDITS_CH = 40 , VC0_TOTAL_CREDITS_CD = 211 , VC0_CPL_INFINITE = TRUE , BAR0 = FFE00000 , BAR1 = FFE00000 , BAR2 = 00000000 , BAR3 = 00000000 , BAR4 = 00000000 , BAR5 = 00000000 , EXPANSION_ROM = 000000 , USR_CFG = FALSE , USR_EXT_CFG = FALSE , DEV_CAP_MAX_PAYLOAD_SUPPORTED = 1 , CLASS_CODE = FFFFFF , CARDBUS_CIS_POINTER = 00000000 , PCIE_CAP_CAPABILITY_VERSION = 1 , PCIE_CAP_DEVICE_PORT_TYPE = 0 , DEV_CAP_PHANTOM_FUNCTIONS_SUPPORT = 0 , DEV_CAP_EXT_TAG_SUPPORTED = FALSE , DEV_CAP_ENDPOINT_L0S_LATENCY = 7 , DEV_CAP_ENDPOINT_L1_LATENCY = 7 , LINK_CAP_ASPM_SUPPORT = 1 , MSI_CAP_MULTIMSGCAP = 0 , MSI_CAP_MULTIMSG_EXTENSION = 0 , LINK_STATUS_SLOT_CLOCK_CONFIG = TRUE , ENABLE_RX_TD_ECRC_TRIM = TRUE , DISABLE_SCRAMBLING = FALSE , PM_CAP_DSI = FALSE , PM_CAP_D1SUPPORT = TRUE , PM_CAP_D2SUPPORT = TRUE , PM_CAP_PMESUPPORT = 0F , PM_DATA0 = 00 , PM_DATA_SCALE0 = 0 , PM_DATA1 = 00 , PM_DATA_SCALE1 = 0 , PM_DATA2 = 00 , PM_DATA_SCALE2 = 0 , PM_DATA3 = 00 , PM_DATA_SCALE3 = 0 , PM_DATA4 = 00 , PM_DATA_SCALE4 = 0 , PM_DATA5 = 00 , PM_DATA_SCALE5 = 0 , PM_DATA6 = 00 , PM_DATA_SCALE6 = 0 , PM_DATA7 = 00 , PM_DATA_SCALE7 = 0 , PCIE_GENERIC = 000010101111 , GTP_SEL = 0 , CFG_VEN_ID = 4953 , CFG_DEV_ID = 5507 , CFG_REV_ID = 10 , CFG_SUBSYS_VEN_ID = 4953 , CFG_SUBSYS_ID = 0008 , REF_CLK_FREQ = 1} " |

Component Instantiations | |

| gt_refclk_bufio2 | BUFIO2 |

| pll_base_i | PLL_BASE |

| mgt_bufg | BUFG |

| mgt2x_bufg | BUFG |

| phy_bufg | BUFG |

| pcie_bram_top | pcie_bram_top_s6 <Entity pcie_bram_top_s6> |

| GT_i | GTPA1_DUAL_WRAPPER <Entity GTPA1_DUAL_WRAPPER> |

| PCIE_A1_inst | PCIE_A1 |

Подробное описание

См. определение в файле cl_s6pcie_m2.vhd строка 246

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/source_s6/cl_s6pcie_m2.vhd

1.7.4

1.7.4