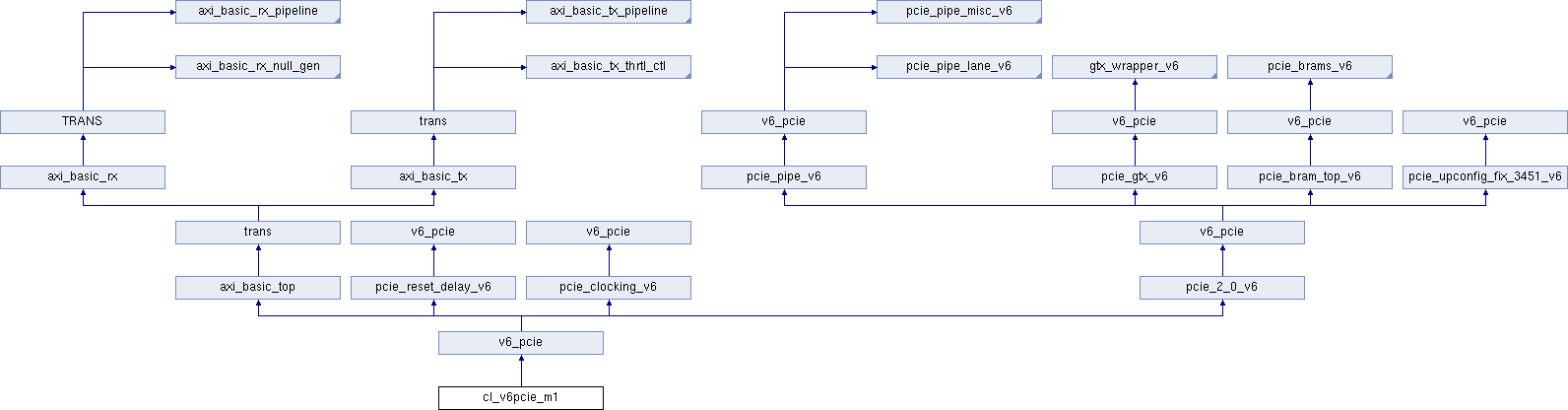

Граф наследования:cl_v6pcie_m1:

Architectures | |

| v6_pcie | Architecture |

Libraries | |

| ieee | |

| unisim | |

Packages | |

| std_logic_1164 | |

| std_logic_unsigned | |

| vcomponents | |

Generics | |

| PCIE_DRP_ENABLE | boolean := false |

| ALLOW_X8_GEN2 | boolean := false |

| BAR0 | bit_vector := x " ffe00000 " |

| BAR1 | bit_vector := x " ffe00000 " |

| BAR2 | bit_vector := x " 00000000 " |

| BAR3 | bit_vector := x " 00000000 " |

| BAR4 | bit_vector := x " 00000000 " |

| BAR5 | bit_vector := x " 00000000 " |

| CARDBUS_CIS_POINTER | bit_vector := x " 00000000 " |

| CLASS_CODE | bit_vector := x " ffffff " |

| CMD_INTX_IMPLEMENTED | boolean := true |

| CPL_TIMEOUT_DISABLE_SUPPORTED | boolean := false |

| CPL_TIMEOUT_RANGES_SUPPORTED | bit_vector := x " 2 " |

| DEV_CAP_ENDPOINT_L0S_LATENCY | integer := 0 |

| DEV_CAP_ENDPOINT_L1_LATENCY | integer := 7 |

| DEV_CAP_EXT_TAG_SUPPORTED | boolean := false |

| DEV_CAP_MAX_PAYLOAD_SUPPORTED | integer := 1 |

| DEV_CAP_PHANTOM_FUNCTIONS_SUPPORT | integer := 0 |

| DEVICE_ID | bit_vector := x " 5507 " |

| DISABLE_LANE_REVERSAL | boolean := true |

| DISABLE_SCRAMBLING | boolean := false |

| DSN_BASE_PTR | bit_vector := x " 0 " |

| DSN_CAP_NEXTPTR | bit_vector := x " 000 " |

| DSN_CAP_ON | boolean := false |

| ENABLE_MSG_ROUTE | bit_vector := " 00000000000 " |

| ENABLE_RX_TD_ECRC_TRIM | boolean := true |

| EXPANSION_ROM | bit_vector := x " 00000000 " |

| EXT_CFG_CAP_PTR | bit_vector := x " 3f " |

| EXT_CFG_XP_CAP_PTR | bit_vector := x " 3ff " |

| HEADER_TYPE | bit_vector := x " 00 " |

| INTERRUPT_PIN | bit_vector := x " 1 " |

| LINK_CAP_DLL_LINK_ACTIVE_REPORTING_CAP | boolean := false |

| LINK_CAP_LINK_BANDWIDTH_NOTIFICATION_CAP | boolean := false |

| LINK_CAP_MAX_LINK_SPEED | bit_vector := x " 2 " |

| LINK_CAP_MAX_LINK_WIDTH | bit_vector := x " 04 " |

| LINK_CAP_MAX_LINK_WIDTH_int | integer := 4 |

| LINK_CAP_SURPRISE_DOWN_ERROR_CAPABLE | boolean := false |

| LINK_CTRL2_DEEMPHASIS | boolean := false |

| LINK_CTRL2_HW_AUTONOMOUS_SPEED_DISABLE | boolean := false |

| LINK_CTRL2_TARGET_LINK_SPEED | bit_vector := x " 2 " |

| LINK_STATUS_SLOT_CLOCK_CONFIG | boolean := true |

| LL_ACK_TIMEOUT | bit_vector := x " 0000 " |

| LL_ACK_TIMEOUT_EN | boolean := false |

| LL_ACK_TIMEOUT_FUNC | integer := 0 |

| LL_REPLAY_TIMEOUT | bit_vector := x " 0026 " |

| LL_REPLAY_TIMEOUT_EN | boolean := true |

| LL_REPLAY_TIMEOUT_FUNC | integer := 1 |

| LTSSM_MAX_LINK_WIDTH | bit_vector := x " 04 " |

| MSI_CAP_MULTIMSGCAP | integer := 0 |

| MSI_CAP_MULTIMSG_EXTENSION | integer := 0 |

| MSI_CAP_ON | boolean := false |

| MSI_CAP_PER_VECTOR_MASKING_CAPABLE | boolean := false |

| MSI_CAP_64_BIT_ADDR_CAPABLE | boolean := true |

| MSIX_CAP_ON | boolean := false |

| MSIX_CAP_PBA_BIR | integer := 0 |

| MSIX_CAP_PBA_OFFSET | bit_vector := x " 0 " |

| MSIX_CAP_TABLE_BIR | integer := 0 |

| MSIX_CAP_TABLE_OFFSET | bit_vector := x " 0 " |

| MSIX_CAP_TABLE_SIZE | bit_vector := x " 000 " |

| PCIE_CAP_DEVICE_PORT_TYPE | bit_vector := x " 0 " |

| PCIE_CAP_INT_MSG_NUM | bit_vector := x " 1 " |

| PCIE_CAP_NEXTPTR | bit_vector := x " 00 " |

| PIPE_PIPELINE_STAGES | integer := 0 |

| PM_CAP_DSI | boolean := false |

| PM_CAP_D1SUPPORT | boolean := false |

| PM_CAP_D2SUPPORT | boolean := false |

| PM_CAP_NEXTPTR | bit_vector := x " 60 " |

| PM_CAP_PMESUPPORT | bit_vector := x " 0f " |

| PM_CSR_NOSOFTRST | boolean := true |

| PM_DATA_SCALE0 | bit_vector := x " 0 " |

| PM_DATA_SCALE1 | bit_vector := x " 0 " |

| PM_DATA_SCALE2 | bit_vector := x " 0 " |

| PM_DATA_SCALE3 | bit_vector := x " 0 " |

| PM_DATA_SCALE4 | bit_vector := x " 0 " |

| PM_DATA_SCALE5 | bit_vector := x " 0 " |

| PM_DATA_SCALE6 | bit_vector := x " 0 " |

| PM_DATA_SCALE7 | bit_vector := x " 0 " |

| PM_DATA0 | bit_vector := x " 00 " |

| PM_DATA1 | bit_vector := x " 00 " |

| PM_DATA2 | bit_vector := x " 00 " |

| PM_DATA3 | bit_vector := x " 00 " |

| PM_DATA4 | bit_vector := x " 00 " |

| PM_DATA5 | bit_vector := x " 00 " |

| PM_DATA6 | bit_vector := x " 00 " |

| PM_DATA7 | bit_vector := x " 00 " |

| REF_CLK_FREQ | integer := 0 |

| REVISION_ID | bit_vector := x " 20 " |

| SPARE_BIT0 | integer := 0 |

| SUBSYSTEM_ID | bit_vector := x " 0002 " |

| SUBSYSTEM_VENDOR_ID | bit_vector := x " 4953 " |

| TL_RX_RAM_RADDR_LATENCY | integer := 0 |

| TL_RX_RAM_RDATA_LATENCY | integer := 2 |

| TL_RX_RAM_WRITE_LATENCY | integer := 0 |

| TL_TX_RAM_RADDR_LATENCY | integer := 0 |

| TL_TX_RAM_RDATA_LATENCY | integer := 2 |

| TL_TX_RAM_WRITE_LATENCY | integer := 0 |

| UPCONFIG_CAPABLE | boolean := true |

| USER_CLK_FREQ | integer := 3 |

| VC_BASE_PTR | bit_vector := x " 0 " |

| VC_CAP_NEXTPTR | bit_vector := x " 000 " |

| VC_CAP_ON | boolean := false |

| VC_CAP_REJECT_SNOOP_TRANSACTIONS | boolean := false |

| VC0_CPL_INFINITE | boolean := true |

| VC0_RX_RAM_LIMIT | bit_vector := x " 3ff " |

| VC0_TOTAL_CREDITS_CD | integer := 378 |

| VC0_TOTAL_CREDITS_CH | integer := 36 |

| VC0_TOTAL_CREDITS_NPH | integer := 12 |

| VC0_TOTAL_CREDITS_PD | integer := 32 |

| VC0_TOTAL_CREDITS_PH | integer := 32 |

| VC0_TX_LASTPACKET | integer := 28 |

| VENDOR_ID | bit_vector := x " 4953 " |

| VSEC_BASE_PTR | bit_vector := x " 0 " |

| VSEC_CAP_NEXTPTR | bit_vector := x " 000 " |

| VSEC_CAP_ON | boolean := false |

| AER_BASE_PTR | bit_vector := x " 128 " |

| AER_CAP_ECRC_CHECK_CAPABLE | boolean := false |

| AER_CAP_ECRC_GEN_CAPABLE | boolean := false |

| AER_CAP_ID | bit_vector := x " 0001 " |

| AER_CAP_INT_MSG_NUM_MSI | bit_vector := x " 0a " |

| AER_CAP_INT_MSG_NUM_MSIX | bit_vector := x " 15 " |

| AER_CAP_NEXTPTR | bit_vector := x " 160 " |

| AER_CAP_ON | boolean := false |

| AER_CAP_PERMIT_ROOTERR_UPDATE | boolean := true |

| AER_CAP_VERSION | bit_vector := x " 1 " |

| CAPABILITIES_PTR | bit_vector := x " 40 " |

| CRM_MODULE_RSTS | bit_vector := x " 00 " |

| DEV_CAP_ENABLE_SLOT_PWR_LIMIT_SCALE | boolean := true |

| DEV_CAP_ENABLE_SLOT_PWR_LIMIT_VALUE | boolean := true |

| DEV_CAP_FUNCTION_LEVEL_RESET_CAPABLE | boolean := false |

| DEV_CAP_ROLE_BASED_ERROR | boolean := true |

| DEV_CAP_RSVD_14_12 | integer := 0 |

| DEV_CAP_RSVD_17_16 | integer := 0 |

| DEV_CAP_RSVD_31_29 | integer := 0 |

| DEV_CONTROL_AUX_POWER_SUPPORTED | boolean := false |

| DISABLE_ASPM_L1_TIMER | boolean := false |

| DISABLE_BAR_FILTERING | boolean := false |

| DISABLE_ID_CHECK | boolean := false |

| DISABLE_RX_TC_FILTER | boolean := false |

| DNSTREAM_LINK_NUM | bit_vector := x " 00 " |

| DSN_CAP_ID | bit_vector := x " 0003 " |

| DSN_CAP_VERSION | bit_vector := x " 1 " |

| ENTER_RVRY_EI_L0 | boolean := true |

| INFER_EI | bit_vector := x " 0c " |

| IS_SWITCH | boolean := false |

| LAST_CONFIG_DWORD | bit_vector := x " 3ff " |

| LINK_CAP_ASPM_SUPPORT | integer := 1 |

| LINK_CAP_CLOCK_POWER_MANAGEMENT | boolean := false |

| LINK_CAP_L0S_EXIT_LATENCY_COMCLK_GEN1 | integer := 7 |

| LINK_CAP_L0S_EXIT_LATENCY_COMCLK_GEN2 | integer := 7 |

| LINK_CAP_L0S_EXIT_LATENCY_GEN1 | integer := 7 |

| LINK_CAP_L0S_EXIT_LATENCY_GEN2 | integer := 7 |

| LINK_CAP_L1_EXIT_LATENCY_COMCLK_GEN1 | integer := 7 |

| LINK_CAP_L1_EXIT_LATENCY_COMCLK_GEN2 | integer := 7 |

| LINK_CAP_L1_EXIT_LATENCY_GEN1 | integer := 7 |

| LINK_CAP_L1_EXIT_LATENCY_GEN2 | integer := 7 |

| LINK_CAP_RSVD_23_22 | integer := 0 |

| LINK_CONTROL_RCB | integer := 0 |

| MSI_BASE_PTR | bit_vector := x " 48 " |

| MSI_CAP_ID | bit_vector := x " 05 " |

| MSI_CAP_NEXTPTR | bit_vector := x " 60 " |

| MSIX_BASE_PTR | bit_vector := x " 9c " |

| MSIX_CAP_ID | bit_vector := x " 11 " |

| MSIX_CAP_NEXTPTR | bit_vector := x " 00 " |

| N_FTS_COMCLK_GEN1 | integer := 255 |

| N_FTS_COMCLK_GEN2 | integer := 254 |

| N_FTS_GEN1 | integer := 255 |

| N_FTS_GEN2 | integer := 255 |

| PCIE_BASE_PTR | bit_vector := x " 60 " |

| PCIE_CAP_CAPABILITY_ID | bit_vector := x " 10 " |

| PCIE_CAP_CAPABILITY_VERSION | bit_vector := x " 2 " |

| PCIE_CAP_ON | boolean := true |

| PCIE_CAP_RSVD_15_14 | integer := 0 |

| PCIE_CAP_SLOT_IMPLEMENTED | boolean := false |

| PCIE_REVISION | integer := 2 |

| PGL0_LANE | integer := 0 |

| PGL1_LANE | integer := 1 |

| PGL2_LANE | integer := 2 |

| PGL3_LANE | integer := 3 |

| PGL4_LANE | integer := 4 |

| PGL5_LANE | integer := 5 |

| PGL6_LANE | integer := 6 |

| PGL7_LANE | integer := 7 |

| PL_AUTO_CONFIG | integer := 0 |

| PL_FAST_TRAIN | boolean := false |

| PM_BASE_PTR | bit_vector := x " 40 " |

| PM_CAP_AUXCURRENT | integer := 0 |

| PM_CAP_ID | bit_vector := x " 01 " |

| PM_CAP_ON | boolean := true |

| PM_CAP_PME_CLOCK | boolean := false |

| PM_CAP_RSVD_04 | integer := 0 |

| PM_CAP_VERSION | integer := 3 |

| PM_CSR_BPCCEN | boolean := false |

| PM_CSR_B2B3 | boolean := false |

| RECRC_CHK | integer := 0 |

| RECRC_CHK_TRIM | boolean := false |

| ROOT_CAP_CRS_SW_VISIBILITY | boolean := false |

| SELECT_DLL_IF | boolean := false |

| SLOT_CAP_ATT_BUTTON_PRESENT | boolean := false |

| SLOT_CAP_ATT_INDICATOR_PRESENT | boolean := false |

| SLOT_CAP_ELEC_INTERLOCK_PRESENT | boolean := false |

| SLOT_CAP_HOTPLUG_CAPABLE | boolean := false |

| SLOT_CAP_HOTPLUG_SURPRISE | boolean := false |

| SLOT_CAP_MRL_SENSOR_PRESENT | boolean := false |

| SLOT_CAP_NO_CMD_COMPLETED_SUPPORT | boolean := false |

| SLOT_CAP_PHYSICAL_SLOT_NUM | bit_vector := x " 0000 " |

| SLOT_CAP_POWER_CONTROLLER_PRESENT | boolean := false |

| SLOT_CAP_POWER_INDICATOR_PRESENT | boolean := false |

| SLOT_CAP_SLOT_POWER_LIMIT_SCALE | integer := 0 |

| SLOT_CAP_SLOT_POWER_LIMIT_VALUE | bit_vector := x " 00 " |

| SPARE_BIT1 | integer := 0 |

| SPARE_BIT2 | integer := 0 |

| SPARE_BIT3 | integer := 0 |

| SPARE_BIT4 | integer := 0 |

| SPARE_BIT5 | integer := 0 |

| SPARE_BIT6 | integer := 0 |

| SPARE_BIT7 | integer := 0 |

| SPARE_BIT8 | integer := 0 |

| SPARE_BYTE0 | bit_vector := x " 00 " |

| SPARE_BYTE1 | bit_vector := x " 00 " |

| SPARE_BYTE2 | bit_vector := x " 00 " |

| SPARE_BYTE3 | bit_vector := x " 00 " |

| SPARE_WORD0 | bit_vector := x " 00000000 " |

| SPARE_WORD1 | bit_vector := x " 00000000 " |

| SPARE_WORD2 | bit_vector := x " 00000000 " |

| SPARE_WORD3 | bit_vector := x " 00000000 " |

| TL_RBYPASS | boolean := false |

| TL_TFC_DISABLE | boolean := false |

| TL_TX_CHECKS_DISABLE | boolean := false |

| EXIT_LOOPBACK_ON_EI | boolean := true |

| UPSTREAM_FACING | boolean := true |

| UR_INV_REQ | boolean := true |

| VC_CAP_ID | bit_vector := x " 0002 " |

| VC_CAP_VERSION | bit_vector := x " 1 " |

| VSEC_CAP_HDR_ID | bit_vector := x " 1234 " |

| VSEC_CAP_HDR_LENGTH | bit_vector := x " 018 " |

| VSEC_CAP_HDR_REVISION | bit_vector := x " 1 " |

| VSEC_CAP_ID | bit_vector := x " 000b " |

| VSEC_CAP_IS_LINK_VISIBLE | boolean := true |

| VSEC_CAP_VERSION | bit_vector := x " 1 " |

Ports | |

| pci_exp_txp | out std_logic_vector ( ( link_cap_max_link_width_int- 1 ) downto 0 ) |

| pci_exp_txn | out std_logic_vector ( ( link_cap_max_link_width_int- 1 ) downto 0 ) |

| pci_exp_rxp | in std_logic_vector ( ( link_cap_max_link_width_int- 1 ) downto 0 ) |

| pci_exp_rxn | in std_logic_vector ( ( link_cap_max_link_width_int- 1 ) downto 0 ) |

| user_clk_out | out std_logic |

| user_reset_out | out std_logic |

| user_lnk_up | out std_logic |

| tx_buf_av | out std_logic_vector ( 5 downto 0 ) |

| tx_cfg_req | out std_logic |

| tx_err_drop | out std_logic |

| tx_cfg_gnt | in std_logic |

| rx_np_ok | in std_logic |

| trn_td | in std_logic_vector ( 63 downto 0 ) := ( others = > ' 0 ' ) |

| trn_tsof | in std_logic := ' 0 ' |

| trn_teof | in std_logic := ' 0 ' |

| trn_tsrc_rdy | in std_logic := ' 0 ' |

| trn_tdst_rdy | out std_logic := ' 0 ' |

| trn_tsrc_dsc | in std_logic := ' 0 ' |

| trn_trem | in std_logic_vector ( 0 downto 0 ) := ( others = > ' 0 ' ) |

| trn_terrfwd | in std_logic := ' 0 ' |

| trn_tstr | in std_logic := ' 0 ' |

| trn_tbuf_av | out std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| trn_tecrc_gen | in std_logic := ' 0 ' |

| trn_rd | out std_logic_vector ( 63 downto 0 ) := ( others = > ' 0 ' ) |

| trn_rsof | out std_logic := ' 0 ' |

| trn_reof | out std_logic := ' 0 ' |

| trn_rsrc_rdy | out std_logic := ' 0 ' |

| trn_rdst_rdy | in std_logic := ' 0 ' |

| trn_rsrc_dsc | out std_logic := ' 0 ' |

| trn_rrem | out std_logic_vector ( 0 downto 0 ) := ( others = > ' 0 ' ) |

| trn_rerrfwd | out std_logic := ' 0 ' |

| trn_rbar_hit | out std_logic_vector ( 6 downto 0 ) := ( others = > ' 0 ' ) |

| trn_recrc_err | out std_logic := ' 0 ' |

| fc_cpld | out std_logic_vector ( 11 downto 0 ) |

| fc_cplh | out std_logic_vector ( 7 downto 0 ) |

| fc_npd | out std_logic_vector ( 11 downto 0 ) |

| fc_nph | out std_logic_vector ( 7 downto 0 ) |

| fc_pd | out std_logic_vector ( 11 downto 0 ) |

| fc_ph | out std_logic_vector ( 7 downto 0 ) |

| fc_sel | in std_logic_vector ( 2 downto 0 ) |

| cfg_do | out std_logic_vector ( 31 downto 0 ) |

| cfg_rd_wr_done | out std_logic |

| cfg_di | in std_logic_vector ( 31 downto 0 ) |

| cfg_byte_en | in std_logic_vector ( 3 downto 0 ) |

| cfg_dwaddr | in std_logic_vector ( 9 downto 0 ) |

| cfg_wr_en | in std_logic |

| cfg_rd_en | in std_logic |

| cfg_err_cor | in std_logic |

| cfg_err_ur | in std_logic |

| cfg_err_ecrc | in std_logic |

| cfg_err_cpl_timeout | in std_logic |

| cfg_err_cpl_abort | in std_logic |

| cfg_err_cpl_unexpect | in std_logic |

| cfg_err_posted | in std_logic |

| cfg_err_locked | in std_logic |

| cfg_err_tlp_cpl_header | in std_logic_vector ( 47 downto 0 ) |

| cfg_err_cpl_rdy | out std_logic |

| cfg_interrupt | in std_logic |

| cfg_interrupt_rdy | out std_logic |

| cfg_interrupt_assert | in std_logic |

| cfg_interrupt_di | in std_logic_vector ( 7 downto 0 ) |

| cfg_interrupt_do | out std_logic_vector ( 7 downto 0 ) |

| cfg_interrupt_mmenable | out std_logic_vector ( 2 downto 0 ) |

| cfg_interrupt_msienable | out std_logic |

| cfg_interrupt_msixenable | out std_logic |

| cfg_interrupt_msixfm | out std_logic |

| cfg_turnoff_ok | in std_logic |

| cfg_to_turnoff | out std_logic |

| cfg_trn_pending | in std_logic |

| cfg_pm_wake | in std_logic |

| cfg_bus_number | out std_logic_vector ( 7 downto 0 ) |

| cfg_device_number | out std_logic_vector ( 4 downto 0 ) |

| cfg_function_number | out std_logic_vector ( 2 downto 0 ) |

| cfg_status | out std_logic_vector ( 15 downto 0 ) |

| cfg_command | out std_logic_vector ( 15 downto 0 ) |

| cfg_dstatus | out std_logic_vector ( 15 downto 0 ) |

| cfg_dcommand | out std_logic_vector ( 15 downto 0 ) |

| cfg_lstatus | out std_logic_vector ( 15 downto 0 ) |

| cfg_lcommand | out std_logic_vector ( 15 downto 0 ) |

| cfg_dcommand2 | out std_logic_vector ( 15 downto 0 ) |

| cfg_pcie_link_state | out std_logic_vector ( 2 downto 0 ) |

| cfg_dsn | in std_logic_vector ( 63 downto 0 ) |

| cfg_pmcsr_pme_en | out std_logic |

| cfg_pmcsr_pme_status | out std_logic |

| cfg_pmcsr_powerstate | out std_logic_vector ( 1 downto 0 ) |

| pl_initial_link_width | out std_logic_vector ( 2 downto 0 ) |

| pl_lane_reversal_mode | out std_logic_vector ( 1 downto 0 ) |

| pl_link_gen2_capable | out std_logic |

| pl_link_partner_gen2_supported | out std_logic |

| pl_link_upcfg_capable | out std_logic |

| pl_ltssm_state | out std_logic_vector ( 5 downto 0 ) |

| pl_received_hot_rst | out std_logic |

| pl_sel_link_rate | out std_logic |

| pl_sel_link_width | out std_logic_vector ( 1 downto 0 ) |

| pl_directed_link_auton | in std_logic |

| pl_directed_link_change | in std_logic_vector ( 1 downto 0 ) |

| pl_directed_link_speed | in std_logic |

| pl_directed_link_width | in std_logic_vector ( 1 downto 0 ) |

| pl_upstream_prefer_deemph | in std_logic |

| sys_clk | in std_logic |

| sys_reset | in std_logic |

Подробное описание

См. определение в файле cl_v6pcie_m1.vhd строка 66

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/source_virtex6/cl_v6pcie_m1.vhd

1.7.4

1.7.4