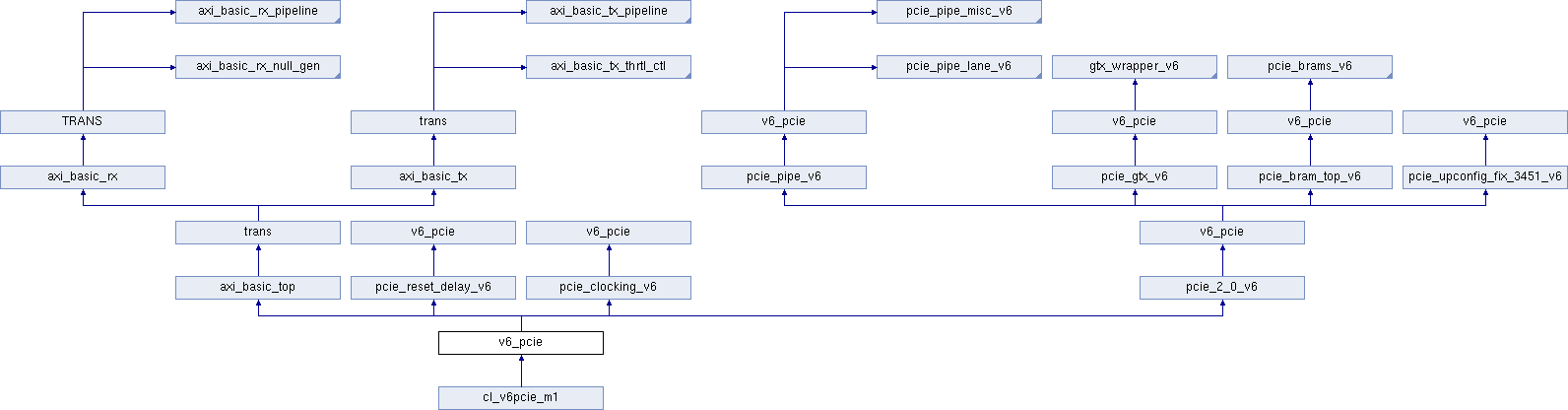

Граф наследования:v6_pcie:

Functions | |

| integer | to_integer ( val_in: in bit_vector ) |

| std_logic | to_stdlogic ( in_val: in boolean ) |

| bit_vector | pad_gen ( in_vec: in bit_vector , op_len: in integer ) |

Processes | |

| PROCESS_47 | ( user_clk ) |

Components | |

| axi_basic_top | <Entity axi_basic_top> |

| pcie_reset_delay_v6 | <Entity pcie_reset_delay_v6> |

| pcie_clocking_v6 | <Entity pcie_clocking_v6> |

| pcie_2_0_v6 | <Entity pcie_2_0_v6> |

Constants | |

| LINK_CAP_MAX_LINK_SPEED_int | integer := to_integer ( LINK_CAP_MAX_LINK_SPEED ) |

Signals | |

| rx_func_level_reset_n | std_logic |

| cfg_msg_received | std_logic |

| cfg_msg_received_pme_to | std_logic |

| cfg_cmd_bme | std_logic |

| cfg_cmd_intdis | std_logic |

| cfg_cmd_io_en | std_logic |

| cfg_cmd_mem_en | std_logic |

| cfg_cmd_serr_en | std_logic |

| cfg_dev_control_aux_power_en | std_logic |

| cfg_dev_control_corr_err_reporting_en | std_logic |

| cfg_dev_control_enable_relaxed_order | std_logic |

| cfg_dev_control_ext_tag_en | std_logic |

| cfg_dev_control_fatal_err_reporting_en | std_logic |

| cfg_dev_control_maxpayload | std_logic_vector ( 2 downto 0 ) |

| cfg_dev_control_max_read_req | std_logic_vector ( 2 downto 0 ) |

| cfg_dev_control_non_fatal_reporting_en | std_logic |

| cfg_dev_control_nosnoop_en | std_logic |

| cfg_dev_control_phantom_en | std_logic |

| cfg_dev_control_ur_err_reporting_en | std_logic |

| cfg_dev_control2_cpltimeout_dis | std_logic |

| cfg_dev_control2_cpltimeout_val | std_logic_vector ( 3 downto 0 ) |

| cfg_dev_status_corr_err_detected | std_logic |

| cfg_dev_status_fatal_err_detected | std_logic |

| cfg_dev_status_nonfatal_err_detected | std_logic |

| cfg_dev_status_ur_detected | std_logic |

| cfg_link_control_auto_bandwidth_int_en | std_logic |

| cfg_link_control_bandwidth_int_en | std_logic |

| cfg_link_control_hw_auto_width_dis | std_logic |

| cfg_link_control_clock_pm_en | std_logic |

| cfg_link_control_extended_sync | std_logic |

| cfg_link_control_common_clock | std_logic |

| cfg_link_control_retrain_link | std_logic |

| cfg_link_control_linkdisable | std_logic |

| cfg_link_control_rcb | std_logic |

| cfg_link_control_aspm_control | std_logic_vector ( 1 downto 0 ) |

| cfg_link_status_autobandwidth_status | std_logic |

| cfg_link_status_bandwidth_status | std_logic |

| cfg_link_status_dll_active | std_logic |

| cfg_link_status_link_training | std_logic |

| cfg_link_status_negotiated_link_width | std_logic_vector ( 3 downto 0 ) |

| cfg_link_status_current_speed | std_logic_vector ( 1 downto 0 ) |

| cfg_msg_data | std_logic_vector ( 15 downto 0 ) |

| sys_reset_n | std_logic |

| sys_reset_n_d | std_logic |

| phy_rdy_n | std_logic |

| TxOutClk | std_logic |

| TxOutClk_bufg | std_logic |

| cfg_bus_number_d | std_logic_vector ( 7 downto 0 ) |

| cfg_device_number_d | std_logic_vector ( 4 downto 0 ) |

| cfg_function_number_d | std_logic_vector ( 2 downto 0 ) |

| trn_rdllp_data | std_logic_vector ( 31 downto 0 ) |

| trn_rdllp_src_rdy_n | std_logic |

| trn_rdllp_src_rdy | std_logic |

| gt_pll_lock | std_logic |

| pipe_clk | std_logic |

| user_clk | std_logic |

| clock_locked | std_logic |

| phy_rdy | std_logic |

| drp_clk | std_logic |

| trn_reset_n_d | std_logic |

| sys_reset_d | std_logic |

| trn_reset_n | std_logic |

| trn_reset_n_int1 | std_logic |

| trn_reset_n_1_d | std_logic |

| trn_lnk_up_n | std_logic |

| trn_lnk_up_n_1 | std_logic |

| user_reset_out_int | std_logic |

| user_lnk_up_int | std_logic |

| user_lnk_up_d | std_logic |

| tx_cfg_req_int | std_logic |

| cfg_pcie_link_state_int | std_logic_vector ( 2 downto 0 ) |

| cfg_pmcsr_powerstate_int | std_logic_vector ( 1 downto 0 ) |

| cfg_to_turnoff_int | std_logic |

| trn_tcfg_req_n | std_logic |

| trn_tcfg_gnt_n | std_logic |

| trn_tcfg_gnt | std_logic |

| trn_terr_drop_n | std_logic |

| trn_rdst_rdy_n | std_logic |

| trn_rnp_ok_n | std_logic |

| trn_tdst_rdy_n | std_logic |

| trn_rrem_n | std_logic |

| trn_trem_n | std_logic |

| trn_rsof_n | std_logic |

| trn_reof_n | std_logic |

| trn_rsrc_rdy_n | std_logic |

| trn_rsrc_dsc_n | std_logic |

| trn_rerrfwd_n | std_logic |

| trn_rbar_hit_n | std_logic_vector ( 6 downto 0 ) |

| trn_recrc_err_n | std_logic |

| trn_tsof_n | std_logic |

| trn_teof_n | std_logic |

| trn_tsrc_rdy_n | std_logic |

| trn_tsrc_dsc_n | std_logic |

| trn_terrfwd_n | std_logic |

| trn_tstr_n | std_logic |

| cfg_rd_wr_done_n | std_logic |

| cfg_err_cpl_rdy_n | std_logic |

| cfg_interrupt_rdy_n | std_logic |

| cfg_byte_en_n | std_logic_vector ( 3 downto 0 ) |

| cfg_err_cor_n | std_logic |

| cfg_err_cpl_abort_n | std_logic |

| cfg_err_cpl_timeout_n | std_logic |

| cfg_err_cpl_unexpect_n | std_logic |

| cfg_err_ecrc_n | std_logic |

| cfg_err_locked_n | std_logic |

| cfg_err_posted_n | std_logic |

| cfg_err_ur_n | std_logic |

| cfg_interrupt_assert_n | std_logic |

| cfg_interrupt_n | std_logic |

| cfg_turnoff_ok_n | std_logic |

| cfg_turnoff_ok_axi | std_logic |

| cfg_pm_wake_n | std_logic |

| cfg_rd_en_n | std_logic |

| cfg_trn_pending_n | std_logic |

| cfg_wr_en_n | std_logic |

| tx_buf_av_int | std_logic_vector ( 5 downto 0 ) |

| pl_sel_link_rate_int | std_logic |

| pl_sel_link_width_int | std_logic_vector ( 1 downto 0 ) |

| LINK_STATUS_SLOT_CLOCK_CONFIG_lstatus | std_logic |

Attributes | |

| CORE_GENERATION_INFO | string |

| CORE_GENERATION_INFO | " cl_v6pcie_m1 , v6_pcie_v2_3 , {LINK_CAP_MAX_LINK_SPEED = 2 , LINK_CAP_MAX_LINK_WIDTH = 04 , PCIE_CAP_DEVICE_PORT_TYPE = 0000 , DEV_CAP_MAX_PAYLOAD_SUPPORTED = 1 , USER_CLK_FREQ = 3 , REF_CLK_FREQ = 0 , MSI_CAP_ON = FALSE , MSI_CAP_MULTIMSGCAP = 0 , MSI_CAP_MULTIMSG_EXTENSION = 0 , MSIX_CAP_ON = FALSE , TL_TX_RAM_RADDR_LATENCY = 0 , TL_TX_RAM_RDATA_LATENCY = 2 , TL_RX_RAM_RADDR_LATENCY = 0 , TL_RX_RAM_RDATA_LATENCY = 2 , TL_RX_RAM_WRITE_LATENCY = 0 , VC0_TX_LASTPACKET = 28 , VC0_RX_RAM_LIMIT = 3FF , VC0_TOTAL_CREDITS_PH = 32 , VC0_TOTAL_CREDITS_PD = 32 , VC0_TOTAL_CREDITS_NPH = 12 , VC0_TOTAL_CREDITS_CH = 36 , VC0_TOTAL_CREDITS_CD = 378 , VC0_CPL_INFINITE = TRUE , DEV_CAP_PHANTOM_FUNCTIONS_SUPPORT = 0 , DEV_CAP_EXT_TAG_SUPPORTED = FALSE , LINK_STATUS_SLOT_CLOCK_CONFIG = TRUE , ENABLE_RX_TD_ECRC_TRIM = TRUE , DISABLE_LANE_REVERSAL = TRUE , DISABLE_SCRAMBLING = FALSE , DSN_CAP_ON = FALSE , PIPE_PIPELINE_STAGES = 0 , REVISION_ID = 20 , VC_CAP_ON = FALSE} " |

Component Instantiations | |

| user_lnk_up_int_i | FDCP |

| trn_lnk_up_n_1_i | FDCP |

| trn_reset_n_i | FDCP |

| trn_reset_n_int_i | FDCP |

| axi_basic_top_i | axi_basic_top <Entity axi_basic_top> |

| pcie_reset_delay_i | pcie_reset_delay_v6 <Entity pcie_reset_delay_v6> |

| pcie_clocking_i | pcie_clocking_v6 <Entity pcie_clocking_v6> |

| pcie_2_0_i | pcie_2_0_v6 <Entity pcie_2_0_v6> |

Подробное описание

См. определение в файле cl_v6pcie_m1.vhd строка 499

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/source_virtex6/cl_v6pcie_m1.vhd

1.7.4

1.7.4