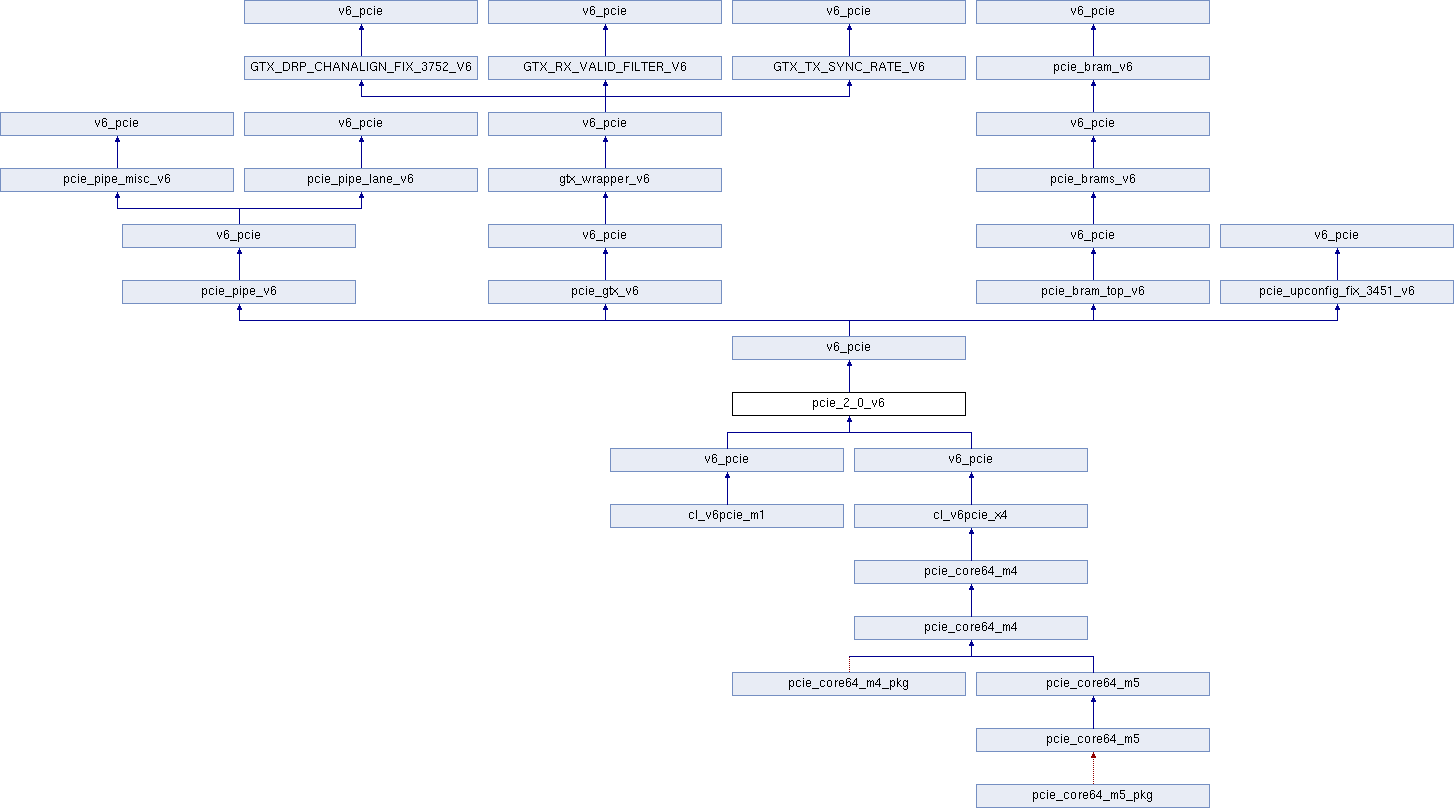

Граф наследования:pcie_2_0_v6:

Architectures | |

| v6_pcie | Architecture |

Libraries | |

| ieee | |

| unisim | |

Packages | |

| std_logic_1164 | |

| std_logic_unsigned | |

| vcomponents | |

Generics | |

| TCQ | integer := 1 |

| REF_CLK_FREQ | integer := 0 |

| PIPE_PIPELINE_STAGES | integer := 0 |

| LINK_CAP_MAX_LINK_WIDTH_int | integer := 8 |

| AER_BASE_PTR | bit_vector := x " 128 " |

| AER_CAP_ECRC_CHECK_CAPABLE | boolean := false |

| AER_CAP_ECRC_GEN_CAPABLE | boolean := false |

| AER_CAP_ID | bit_vector := x " 0001 " |

| AER_CAP_INT_MSG_NUM_MSI | bit_vector := x " 0a " |

| AER_CAP_INT_MSG_NUM_MSIX | bit_vector := x " 15 " |

| AER_CAP_NEXTPTR | bit_vector := x " 160 " |

| AER_CAP_ON | boolean := false |

| AER_CAP_PERMIT_ROOTERR_UPDATE | boolean := true |

| AER_CAP_VERSION | bit_vector := x " 1 " |

| ALLOW_X8_GEN2 | boolean := false |

| BAR0 | bit_vector := x " ffffff00 " |

| BAR1 | bit_vector := x " ffff0000 " |

| BAR2 | bit_vector := x " ffff000c " |

| BAR3 | bit_vector := x " ffffffff " |

| BAR4 | bit_vector := x " 00000000 " |

| BAR5 | bit_vector := x " 00000000 " |

| CAPABILITIES_PTR | bit_vector := x " 40 " |

| CARDBUS_CIS_POINTER | bit_vector := x " 00000000 " |

| CLASS_CODE | bit_vector := x " 000000 " |

| CMD_INTX_IMPLEMENTED | boolean := true |

| CPL_TIMEOUT_DISABLE_SUPPORTED | boolean := false |

| CPL_TIMEOUT_RANGES_SUPPORTED | bit_vector := x " 0 " |

| CRM_MODULE_RSTS | bit_vector := x " 00 " |

| DEV_CAP_ENABLE_SLOT_PWR_LIMIT_SCALE | boolean := true |

| DEV_CAP_ENABLE_SLOT_PWR_LIMIT_VALUE | boolean := true |

| DEV_CAP_ENDPOINT_L0S_LATENCY | integer := 0 |

| DEV_CAP_ENDPOINT_L1_LATENCY | integer := 0 |

| DEV_CAP_EXT_TAG_SUPPORTED | boolean := true |

| DEV_CAP_FUNCTION_LEVEL_RESET_CAPABLE | boolean := false |

| DEV_CAP_MAX_PAYLOAD_SUPPORTED | integer := 2 |

| DEV_CAP_PHANTOM_FUNCTIONS_SUPPORT | integer := 0 |

| DEV_CAP_ROLE_BASED_ERROR | boolean := true |

| DEV_CAP_RSVD_14_12 | integer := 0 |

| DEV_CAP_RSVD_17_16 | integer := 0 |

| DEV_CAP_RSVD_31_29 | integer := 0 |

| DEV_CONTROL_AUX_POWER_SUPPORTED | boolean := false |

| DEVICE_ID | bit_vector := x " 0007 " |

| DISABLE_ASPM_L1_TIMER | boolean := false |

| DISABLE_BAR_FILTERING | boolean := false |

| DISABLE_ID_CHECK | boolean := false |

| DISABLE_LANE_REVERSAL | boolean := false |

| DISABLE_RX_TC_FILTER | boolean := false |

| DISABLE_SCRAMBLING | boolean := false |

| DNSTREAM_LINK_NUM | bit_vector := x " 00 " |

| DSN_BASE_PTR | bit_vector := x " 100 " |

| DSN_CAP_ID | bit_vector := x " 0003 " |

| DSN_CAP_NEXTPTR | bit_vector := x " 000 " |

| DSN_CAP_ON | boolean := true |

| DSN_CAP_VERSION | bit_vector := x " 1 " |

| ENABLE_MSG_ROUTE | bit_vector := x " 000 " |

| ENABLE_RX_TD_ECRC_TRIM | boolean := false |

| ENTER_RVRY_EI_L0 | boolean := true |

| EXPANSION_ROM | bit_vector := x " fffff001 " |

| EXT_CFG_CAP_PTR | bit_vector := x " 3f " |

| EXT_CFG_XP_CAP_PTR | bit_vector := x " 3ff " |

| HEADER_TYPE | bit_vector := x " 00 " |

| INFER_EI | bit_vector := x " 00 " |

| INTERRUPT_PIN | bit_vector := x " 01 " |

| IS_SWITCH | boolean := false |

| LAST_CONFIG_DWORD | bit_vector := x " 042 " |

| LINK_CAP_ASPM_SUPPORT | integer := 1 |

| LINK_CAP_CLOCK_POWER_MANAGEMENT | boolean := false |

| LINK_CAP_DLL_LINK_ACTIVE_REPORTING_CAP | boolean := false |

| LINK_CAP_L0S_EXIT_LATENCY_COMCLK_GEN1 | integer := 7 |

| LINK_CAP_L0S_EXIT_LATENCY_COMCLK_GEN2 | integer := 7 |

| LINK_CAP_L0S_EXIT_LATENCY_GEN1 | integer := 7 |

| LINK_CAP_L0S_EXIT_LATENCY_GEN2 | integer := 7 |

| LINK_CAP_L1_EXIT_LATENCY_COMCLK_GEN1 | integer := 7 |

| LINK_CAP_L1_EXIT_LATENCY_COMCLK_GEN2 | integer := 7 |

| LINK_CAP_L1_EXIT_LATENCY_GEN1 | integer := 7 |

| LINK_CAP_L1_EXIT_LATENCY_GEN2 | integer := 7 |

| LINK_CAP_LINK_BANDWIDTH_NOTIFICATION_CAP | boolean := false |

| LINK_CAP_MAX_LINK_SPEED | bit_vector := x " 1 " |

| LINK_CAP_MAX_LINK_WIDTH | bit_vector := x " 08 " |

| LINK_CAP_RSVD_23_22 | integer := 0 |

| LINK_CAP_SURPRISE_DOWN_ERROR_CAPABLE | boolean := false |

| LINK_CONTROL_RCB | integer := 0 |

| LINK_CTRL2_DEEMPHASIS | boolean := false |

| LINK_CTRL2_HW_AUTONOMOUS_SPEED_DISABLE | boolean := false |

| LINK_CTRL2_TARGET_LINK_SPEED | bit_vector := x " 2 " |

| LINK_STATUS_SLOT_CLOCK_CONFIG | boolean := true |

| LL_ACK_TIMEOUT | bit_vector := x " 0000 " |

| LL_ACK_TIMEOUT_EN | boolean := false |

| LL_ACK_TIMEOUT_FUNC | integer := 0 |

| LL_REPLAY_TIMEOUT | bit_vector := x " 0000 " |

| LL_REPLAY_TIMEOUT_EN | boolean := false |

| LL_REPLAY_TIMEOUT_FUNC | integer := 0 |

| LTSSM_MAX_LINK_WIDTH | bit_vector := x " 01 " |

| MSI_BASE_PTR | bit_vector := x " 48 " |

| MSI_CAP_ID | bit_vector := x " 05 " |

| MSI_CAP_MULTIMSGCAP | integer := 0 |

| MSI_CAP_MULTIMSG_EXTENSION | integer := 0 |

| MSI_CAP_NEXTPTR | bit_vector := x " 60 " |

| MSI_CAP_ON | boolean := false |

| MSI_CAP_PER_VECTOR_MASKING_CAPABLE | boolean := true |

| MSI_CAP_64_BIT_ADDR_CAPABLE | boolean := true |

| MSIX_BASE_PTR | bit_vector := x " 9c " |

| MSIX_CAP_ID | bit_vector := x " 11 " |

| MSIX_CAP_NEXTPTR | bit_vector := x " 00 " |

| MSIX_CAP_ON | boolean := false |

| MSIX_CAP_PBA_BIR | integer := 0 |

| MSIX_CAP_PBA_OFFSET | bit_vector := x " 00000050 " |

| MSIX_CAP_TABLE_BIR | integer := 0 |

| MSIX_CAP_TABLE_OFFSET | bit_vector := x " 00000040 " |

| MSIX_CAP_TABLE_SIZE | bit_vector := x " 000 " |

| N_FTS_COMCLK_GEN1 | integer := 255 |

| N_FTS_COMCLK_GEN2 | integer := 255 |

| N_FTS_GEN1 | integer := 255 |

| N_FTS_GEN2 | integer := 255 |

| PCIE_BASE_PTR | bit_vector := x " 60 " |

| PCIE_CAP_CAPABILITY_ID | bit_vector := x " 10 " |

| PCIE_CAP_CAPABILITY_VERSION | bit_vector := x " 2 " |

| PCIE_CAP_DEVICE_PORT_TYPE | bit_vector := x " 0 " |

| PCIE_CAP_INT_MSG_NUM | bit_vector := x " 00 " |

| PCIE_CAP_NEXTPTR | bit_vector := x " 00 " |

| PCIE_CAP_ON | boolean := true |

| PCIE_CAP_RSVD_15_14 | integer := 0 |

| PCIE_CAP_SLOT_IMPLEMENTED | boolean := false |

| PCIE_REVISION | integer := 2 |

| PGL0_LANE | integer := 0 |

| PGL1_LANE | integer := 1 |

| PGL2_LANE | integer := 2 |

| PGL3_LANE | integer := 3 |

| PGL4_LANE | integer := 4 |

| PGL5_LANE | integer := 5 |

| PGL6_LANE | integer := 6 |

| PGL7_LANE | integer := 7 |

| PL_AUTO_CONFIG | integer := 0 |

| PL_FAST_TRAIN | boolean := false |

| PM_BASE_PTR | bit_vector := x " 40 " |

| PM_CAP_AUXCURRENT | integer := 0 |

| PM_CAP_DSI | boolean := false |

| PM_CAP_D1SUPPORT | boolean := true |

| PM_CAP_D2SUPPORT | boolean := true |

| PM_CAP_ID | bit_vector := x " 11 " |

| PM_CAP_NEXTPTR | bit_vector := x " 48 " |

| PM_CAP_ON | boolean := true |

| PM_CAP_PME_CLOCK | boolean := false |

| PM_CAP_PMESUPPORT | bit_vector := x " 0f " |

| PM_CAP_RSVD_04 | integer := 0 |

| PM_CAP_VERSION | integer := 3 |

| PM_CSR_BPCCEN | boolean := false |

| PM_CSR_B2B3 | boolean := false |

| PM_CSR_NOSOFTRST | boolean := true |

| PM_DATA0 | bit_vector := x " 01 " |

| PM_DATA1 | bit_vector := x " 01 " |

| PM_DATA2 | bit_vector := x " 01 " |

| PM_DATA3 | bit_vector := x " 01 " |

| PM_DATA4 | bit_vector := x " 01 " |

| PM_DATA5 | bit_vector := x " 01 " |

| PM_DATA6 | bit_vector := x " 01 " |

| PM_DATA7 | bit_vector := x " 01 " |

| PM_DATA_SCALE0 | bit_vector := x " 1 " |

| PM_DATA_SCALE1 | bit_vector := x " 1 " |

| PM_DATA_SCALE2 | bit_vector := x " 1 " |

| PM_DATA_SCALE3 | bit_vector := x " 1 " |

| PM_DATA_SCALE4 | bit_vector := x " 1 " |

| PM_DATA_SCALE5 | bit_vector := x " 1 " |

| PM_DATA_SCALE6 | bit_vector := x " 1 " |

| PM_DATA_SCALE7 | bit_vector := x " 1 " |

| RECRC_CHK | integer := 0 |

| RECRC_CHK_TRIM | boolean := false |

| REVISION_ID | bit_vector := x " 00 " |

| ROOT_CAP_CRS_SW_VISIBILITY | boolean := false |

| SELECT_DLL_IF | boolean := false |

| SLOT_CAP_ATT_BUTTON_PRESENT | boolean := false |

| SLOT_CAP_ATT_INDICATOR_PRESENT | boolean := false |

| SLOT_CAP_ELEC_INTERLOCK_PRESENT | boolean := false |

| SLOT_CAP_HOTPLUG_CAPABLE | boolean := false |

| SLOT_CAP_HOTPLUG_SURPRISE | boolean := false |

| SLOT_CAP_MRL_SENSOR_PRESENT | boolean := false |

| SLOT_CAP_NO_CMD_COMPLETED_SUPPORT | boolean := false |

| SLOT_CAP_PHYSICAL_SLOT_NUM | bit_vector := x " 0000 " |

| SLOT_CAP_POWER_CONTROLLER_PRESENT | boolean := false |

| SLOT_CAP_POWER_INDICATOR_PRESENT | boolean := false |

| SLOT_CAP_SLOT_POWER_LIMIT_SCALE | integer := 0 |

| SLOT_CAP_SLOT_POWER_LIMIT_VALUE | bit_vector := x " 00 " |

| SPARE_BIT0 | integer := 0 |

| SPARE_BIT1 | integer := 0 |

| SPARE_BIT2 | integer := 0 |

| SPARE_BIT3 | integer := 0 |

| SPARE_BIT4 | integer := 0 |

| SPARE_BIT5 | integer := 0 |

| SPARE_BIT6 | integer := 0 |

| SPARE_BIT7 | integer := 0 |

| SPARE_BIT8 | integer := 0 |

| SPARE_BYTE0 | bit_vector := x " 00 " |

| SPARE_BYTE1 | bit_vector := x " 00 " |

| SPARE_BYTE2 | bit_vector := x " 00 " |

| SPARE_BYTE3 | bit_vector := x " 00 " |

| SPARE_WORD0 | bit_vector := x " 00000000 " |

| SPARE_WORD1 | bit_vector := x " 00000000 " |

| SPARE_WORD2 | bit_vector := x " 00000000 " |

| SPARE_WORD3 | bit_vector := x " 00000000 " |

| SUBSYSTEM_ID | bit_vector := x " 0007 " |

| SUBSYSTEM_VENDOR_ID | bit_vector := x " 10ee " |

| TL_RBYPASS | boolean := false |

| TL_RX_RAM_RADDR_LATENCY | integer := 0 |

| TL_RX_RAM_RDATA_LATENCY | integer := 2 |

| TL_RX_RAM_WRITE_LATENCY | integer := 0 |

| TL_TFC_DISABLE | boolean := false |

| TL_TX_CHECKS_DISABLE | boolean := false |

| TL_TX_RAM_RADDR_LATENCY | integer := 0 |

| TL_TX_RAM_RDATA_LATENCY | integer := 2 |

| TL_TX_RAM_WRITE_LATENCY | integer := 0 |

| UPCONFIG_CAPABLE | boolean := true |

| UPSTREAM_FACING | boolean := true |

| UR_INV_REQ | boolean := true |

| USER_CLK_FREQ | integer := 3 |

| EXIT_LOOPBACK_ON_EI | boolean := true |

| VC_BASE_PTR | bit_vector := x " 10c " |

| VC_CAP_ID | bit_vector := x " 0002 " |

| VC_CAP_NEXTPTR | bit_vector := x " 000 " |

| VC_CAP_ON | boolean := false |

| VC_CAP_REJECT_SNOOP_TRANSACTIONS | boolean := false |

| VC_CAP_VERSION | bit_vector := x " 1 " |

| VC0_CPL_INFINITE | boolean := true |

| VC0_RX_RAM_LIMIT | bit_vector := x " 03ff " |

| VC0_TOTAL_CREDITS_CD | integer := 127 |

| VC0_TOTAL_CREDITS_CH | integer := 31 |

| VC0_TOTAL_CREDITS_NPH | integer := 12 |

| VC0_TOTAL_CREDITS_PD | integer := 288 |

| VC0_TOTAL_CREDITS_PH | integer := 32 |

| VC0_TX_LASTPACKET | integer := 31 |

| VENDOR_ID | bit_vector := x " 10ee " |

| VSEC_BASE_PTR | bit_vector := x " 160 " |

| VSEC_CAP_HDR_ID | bit_vector := x " 1234 " |

| VSEC_CAP_HDR_LENGTH | bit_vector := x " 018 " |

| VSEC_CAP_HDR_REVISION | bit_vector := x " 1 " |

| VSEC_CAP_ID | bit_vector := x " 000b " |

| VSEC_CAP_IS_LINK_VISIBLE | boolean := true |

| VSEC_CAP_NEXTPTR | bit_vector := x " 000 " |

| VSEC_CAP_ON | boolean := false |

| VSEC_CAP_VERSION | bit_vector := x " 1 " |

Ports | |

| PCIEXPRXN | in std_logic_vector ( ( link_cap_max_link_width_int- 1 ) downto 0 ) |

| PCIEXPRXP | in std_logic_vector ( ( link_cap_max_link_width_int- 1 ) downto 0 ) |

| PCIEXPTXN | out std_logic_vector ( ( link_cap_max_link_width_int- 1 ) downto 0 ) |

| PCIEXPTXP | out std_logic_vector ( ( link_cap_max_link_width_int- 1 ) downto 0 ) |

| SYSCLK | in std_logic |

| FUNDRSTN | in std_logic |

| TRNLNKUPN | out std_logic |

| PHYRDYN | out std_logic |

| USERRSTN | out std_logic |

| RECEIVEDFUNCLVLRSTN | out std_logic |

| LNKCLKEN | out std_logic |

| SYSRSTN | in std_logic |

| PLRSTN | in std_logic |

| DLRSTN | in std_logic |

| TLRSTN | in std_logic |

| FUNCLVLRSTN | in std_logic |

| CMRSTN | in std_logic |

| CMSTICKYRSTN | in std_logic |

| TRNRBARHITN | out std_logic_vector ( 6 downto 0 ) |

| TRNRD | out std_logic_vector ( 63 downto 0 ) |

| TRNRECRCERRN | out std_logic |

| TRNREOFN | out std_logic |

| TRNRERRFWDN | out std_logic |

| TRNRREMN | out std_logic |

| TRNRSOFN | out std_logic |

| TRNRSRCDSCN | out std_logic |

| TRNRSRCRDYN | out std_logic |

| TRNRDSTRDYN | in std_logic |

| TRNRNPOKN | in std_logic |

| TRNRDLLPDATA | out std_logic_vector ( 31 downto 0 ) |

| TRNRDLLPSRCRDYN | out std_logic |

| TRNTBUFAV | out std_logic_vector ( 5 downto 0 ) |

| TRNTCFGREQN | out std_logic |

| TRNTDLLPDSTRDYN | out std_logic |

| TRNTDSTRDYN | out std_logic |

| TRNTERRDROPN | out std_logic |

| TRNTCFGGNTN | in std_logic |

| TRNTD | in std_logic_vector ( 63 downto 0 ) |

| TRNTDLLPDATA | in std_logic_vector ( 31 downto 0 ) |

| TRNTDLLPSRCRDYN | in std_logic |

| TRNTECRCGENN | in std_logic |

| TRNTEOFN | in std_logic |

| TRNTERRFWDN | in std_logic |

| TRNTREMN | in std_logic |

| TRNTSOFN | in std_logic |

| TRNTSRCDSCN | in std_logic |

| TRNTSRCRDYN | in std_logic |

| TRNTSTRN | in std_logic |

| TRNFCCPLD | out std_logic_vector ( 11 downto 0 ) |

| TRNFCCPLH | out std_logic_vector ( 7 downto 0 ) |

| TRNFCNPD | out std_logic_vector ( 11 downto 0 ) |

| TRNFCNPH | out std_logic_vector ( 7 downto 0 ) |

| TRNFCPD | out std_logic_vector ( 11 downto 0 ) |

| TRNFCPH | out std_logic_vector ( 7 downto 0 ) |

| TRNFCSEL | in std_logic_vector ( 2 downto 0 ) |

| CFGAERECRCCHECKEN | out std_logic |

| CFGAERECRCGENEN | out std_logic |

| CFGCOMMANDBUSMASTERENABLE | out std_logic |

| CFGCOMMANDINTERRUPTDISABLE | out std_logic |

| CFGCOMMANDIOENABLE | out std_logic |

| CFGCOMMANDMEMENABLE | out std_logic |

| CFGCOMMANDSERREN | out std_logic |

| CFGDEVCONTROLAUXPOWEREN | out std_logic |

| CFGDEVCONTROLCORRERRREPORTINGEN | out std_logic |

| CFGDEVCONTROLENABLERO | out std_logic |

| CFGDEVCONTROLEXTTAGEN | out std_logic |

| CFGDEVCONTROLFATALERRREPORTINGEN | out std_logic |

| CFGDEVCONTROLMAXPAYLOAD | out std_logic_vector ( 2 downto 0 ) |

| CFGDEVCONTROLMAXREADREQ | out std_logic_vector ( 2 downto 0 ) |

| CFGDEVCONTROLNONFATALREPORTINGEN | out std_logic |

| CFGDEVCONTROLNOSNOOPEN | out std_logic |

| CFGDEVCONTROLPHANTOMEN | out std_logic |

| CFGDEVCONTROLURERRREPORTINGEN | out std_logic |

| CFGDEVCONTROL2CPLTIMEOUTDIS | out std_logic |

| CFGDEVCONTROL2CPLTIMEOUTVAL | out std_logic_vector ( 3 downto 0 ) |

| CFGDEVSTATUSCORRERRDETECTED | out std_logic |

| CFGDEVSTATUSFATALERRDETECTED | out std_logic |

| CFGDEVSTATUSNONFATALERRDETECTED | out std_logic |

| CFGDEVSTATUSURDETECTED | out std_logic |

| CFGDO | out std_logic_vector ( 31 downto 0 ) |

| CFGERRAERHEADERLOGSETN | out std_logic |

| CFGERRCPLRDYN | out std_logic |

| CFGINTERRUPTDO | out std_logic_vector ( 7 downto 0 ) |

| CFGINTERRUPTMMENABLE | out std_logic_vector ( 2 downto 0 ) |

| CFGINTERRUPTMSIENABLE | out std_logic |

| CFGINTERRUPTMSIXENABLE | out std_logic |

| CFGINTERRUPTMSIXFM | out std_logic |

| CFGINTERRUPTRDYN | out std_logic |

| CFGLINKCONTROLRCB | out std_logic |

| CFGLINKCONTROLASPMCONTROL | out std_logic_vector ( 1 downto 0 ) |

| CFGLINKCONTROLAUTOBANDWIDTHINTEN | out std_logic |

| CFGLINKCONTROLBANDWIDTHINTEN | out std_logic |

| CFGLINKCONTROLCLOCKPMEN | out std_logic |

| CFGLINKCONTROLCOMMONCLOCK | out std_logic |

| CFGLINKCONTROLEXTENDEDSYNC | out std_logic |

| CFGLINKCONTROLHWAUTOWIDTHDIS | out std_logic |

| CFGLINKCONTROLLINKDISABLE | out std_logic |

| CFGLINKCONTROLRETRAINLINK | out std_logic |

| CFGLINKSTATUSAUTOBANDWIDTHSTATUS | out std_logic |

| CFGLINKSTATUSBANDWITHSTATUS | out std_logic |

| CFGLINKSTATUSCURRENTSPEED | out std_logic_vector ( 1 downto 0 ) |

| CFGLINKSTATUSDLLACTIVE | out std_logic |

| CFGLINKSTATUSLINKTRAINING | out std_logic |

| CFGLINKSTATUSNEGOTIATEDWIDTH | out std_logic_vector ( 3 downto 0 ) |

| CFGMSGDATA | out std_logic_vector ( 15 downto 0 ) |

| CFGMSGRECEIVED | out std_logic |

| CFGMSGRECEIVEDASSERTINTA | out std_logic |

| CFGMSGRECEIVEDASSERTINTB | out std_logic |

| CFGMSGRECEIVEDASSERTINTC | out std_logic |

| CFGMSGRECEIVEDASSERTINTD | out std_logic |

| CFGMSGRECEIVEDDEASSERTINTA | out std_logic |

| CFGMSGRECEIVEDDEASSERTINTB | out std_logic |

| CFGMSGRECEIVEDDEASSERTINTC | out std_logic |

| CFGMSGRECEIVEDDEASSERTINTD | out std_logic |

| CFGMSGRECEIVEDERRCOR | out std_logic |

| CFGMSGRECEIVEDERRFATAL | out std_logic |

| CFGMSGRECEIVEDERRNONFATAL | out std_logic |

| CFGMSGRECEIVEDPMASNAK | out std_logic |

| CFGMSGRECEIVEDPMETO | out std_logic |

| CFGMSGRECEIVEDPMETOACK | out std_logic |

| CFGMSGRECEIVEDPMPME | out std_logic |

| CFGMSGRECEIVEDSETSLOTPOWERLIMIT | out std_logic |

| CFGMSGRECEIVEDUNLOCK | out std_logic |

| CFGPCIELINKSTATE | out std_logic_vector ( 2 downto 0 ) |

| CFGPMCSRPMEEN | out std_logic |

| CFGPMCSRPMESTATUS | out std_logic |

| CFGPMCSRPOWERSTATE | out std_logic_vector ( 1 downto 0 ) |

| CFGPMRCVASREQL1N | out std_logic |

| CFGPMRCVENTERL1N | out std_logic |

| CFGPMRCVENTERL23N | out std_logic |

| CFGPMRCVREQACKN | out std_logic |

| CFGRDWRDONEN | out std_logic |

| CFGSLOTCONTROLELECTROMECHILCTLPULSE | out std_logic |

| CFGTRANSACTION | out std_logic |

| CFGTRANSACTIONADDR | out std_logic_vector ( 6 downto 0 ) |

| CFGTRANSACTIONTYPE | out std_logic |

| CFGVCTCVCMAP | out std_logic_vector ( 6 downto 0 ) |

| CFGBYTEENN | in std_logic_vector ( 3 downto 0 ) |

| CFGDI | in std_logic_vector ( 31 downto 0 ) |

| CFGDSBUSNUMBER | in std_logic_vector ( 7 downto 0 ) |

| CFGDSDEVICENUMBER | in std_logic_vector ( 4 downto 0 ) |

| CFGDSFUNCTIONNUMBER | in std_logic_vector ( 2 downto 0 ) |

| CFGDSN | in std_logic_vector ( 63 downto 0 ) |

| CFGDWADDR | in std_logic_vector ( 9 downto 0 ) |

| CFGERRACSN | in std_logic |

| CFGERRAERHEADERLOG | in std_logic_vector ( 127 downto 0 ) |

| CFGERRCORN | in std_logic |

| CFGERRCPLABORTN | in std_logic |

| CFGERRCPLTIMEOUTN | in std_logic |

| CFGERRCPLUNEXPECTN | in std_logic |

| CFGERRECRCN | in std_logic |

| CFGERRLOCKEDN | in std_logic |

| CFGERRPOSTEDN | in std_logic |

| CFGERRTLPCPLHEADER | in std_logic_vector ( 47 downto 0 ) |

| CFGERRURN | in std_logic |

| CFGINTERRUPTASSERTN | in std_logic |

| CFGINTERRUPTDI | in std_logic_vector ( 7 downto 0 ) |

| CFGINTERRUPTN | in std_logic |

| CFGPMDIRECTASPML1N | in std_logic |

| CFGPMSENDPMACKN | in std_logic |

| CFGPMSENDPMETON | in std_logic |

| CFGPMSENDPMNAKN | in std_logic |

| CFGPMTURNOFFOKN | in std_logic |

| CFGPMWAKEN | in std_logic |

| CFGPORTNUMBER | in std_logic_vector ( 7 downto 0 ) |

| CFGRDENN | in std_logic |

| CFGTRNPENDINGN | in std_logic |

| CFGWRENN | in std_logic |

| CFGWRREADONLYN | in std_logic |

| CFGWRRW1CASRWN | in std_logic |

| PLINITIALLINKWIDTH | out std_logic_vector ( 2 downto 0 ) |

| PLLANEREVERSALMODE | out std_logic_vector ( 1 downto 0 ) |

| PLLINKGEN2CAP | out std_logic |

| PLLINKPARTNERGEN2SUPPORTED | out std_logic |

| PLLINKUPCFGCAP | out std_logic |

| PLLTSSMSTATE | out std_logic_vector ( 5 downto 0 ) |

| PLPHYLNKUPN | out std_logic |

| PLRECEIVEDHOTRST | out std_logic |

| PLRXPMSTATE | out std_logic_vector ( 1 downto 0 ) |

| PLSELLNKRATE | out std_logic |

| PLSELLNKWIDTH | out std_logic_vector ( 1 downto 0 ) |

| PLTXPMSTATE | out std_logic_vector ( 2 downto 0 ) |

| PLDIRECTEDLINKAUTON | in std_logic |

| PLDIRECTEDLINKCHANGE | in std_logic_vector ( 1 downto 0 ) |

| PLDIRECTEDLINKSPEED | in std_logic |

| PLDIRECTEDLINKWIDTH | in std_logic_vector ( 1 downto 0 ) |

| PLDOWNSTREAMDEEMPHSOURCE | in std_logic |

| PLUPSTREAMPREFERDEEMPH | in std_logic |

| PLTRANSMITHOTRST | in std_logic |

| DBGSCLRA | out std_logic |

| DBGSCLRB | out std_logic |

| DBGSCLRC | out std_logic |

| DBGSCLRD | out std_logic |

| DBGSCLRE | out std_logic |

| DBGSCLRF | out std_logic |

| DBGSCLRG | out std_logic |

| DBGSCLRH | out std_logic |

| DBGSCLRI | out std_logic |

| DBGSCLRJ | out std_logic |

| DBGSCLRK | out std_logic |

| DBGVECA | out std_logic_vector ( 63 downto 0 ) |

| DBGVECB | out std_logic_vector ( 63 downto 0 ) |

| DBGVECC | out std_logic_vector ( 11 downto 0 ) |

| PLDBGVEC | out std_logic_vector ( 11 downto 0 ) |

| DBGMODE | in std_logic_vector ( 1 downto 0 ) |

| DBGSUBMODE | in std_logic |

| PLDBGMODE | in std_logic_vector ( 2 downto 0 ) |

| PCIEDRPDO | out std_logic_vector ( 15 downto 0 ) |

| PCIEDRPDRDY | out std_logic |

| PCIEDRPCLK | in std_logic |

| PCIEDRPDADDR | in std_logic_vector ( 8 downto 0 ) |

| PCIEDRPDEN | in std_logic |

| PCIEDRPDI | in std_logic_vector ( 15 downto 0 ) |

| PCIEDRPDWE | in std_logic |

| GTPLLLOCK | out std_logic |

| PIPECLK | in std_logic |

| USERCLK | in std_logic |

| DRPCLK | in std_logic |

| CLOCKLOCKED | in std_logic |

| TxOutClk | out std_logic |

Подробное описание

См. определение в файле pcie_2_0_v6.vhd строка 66

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/source_virtex6/pcie_2_0_v6.vhd

1.7.4

1.7.4