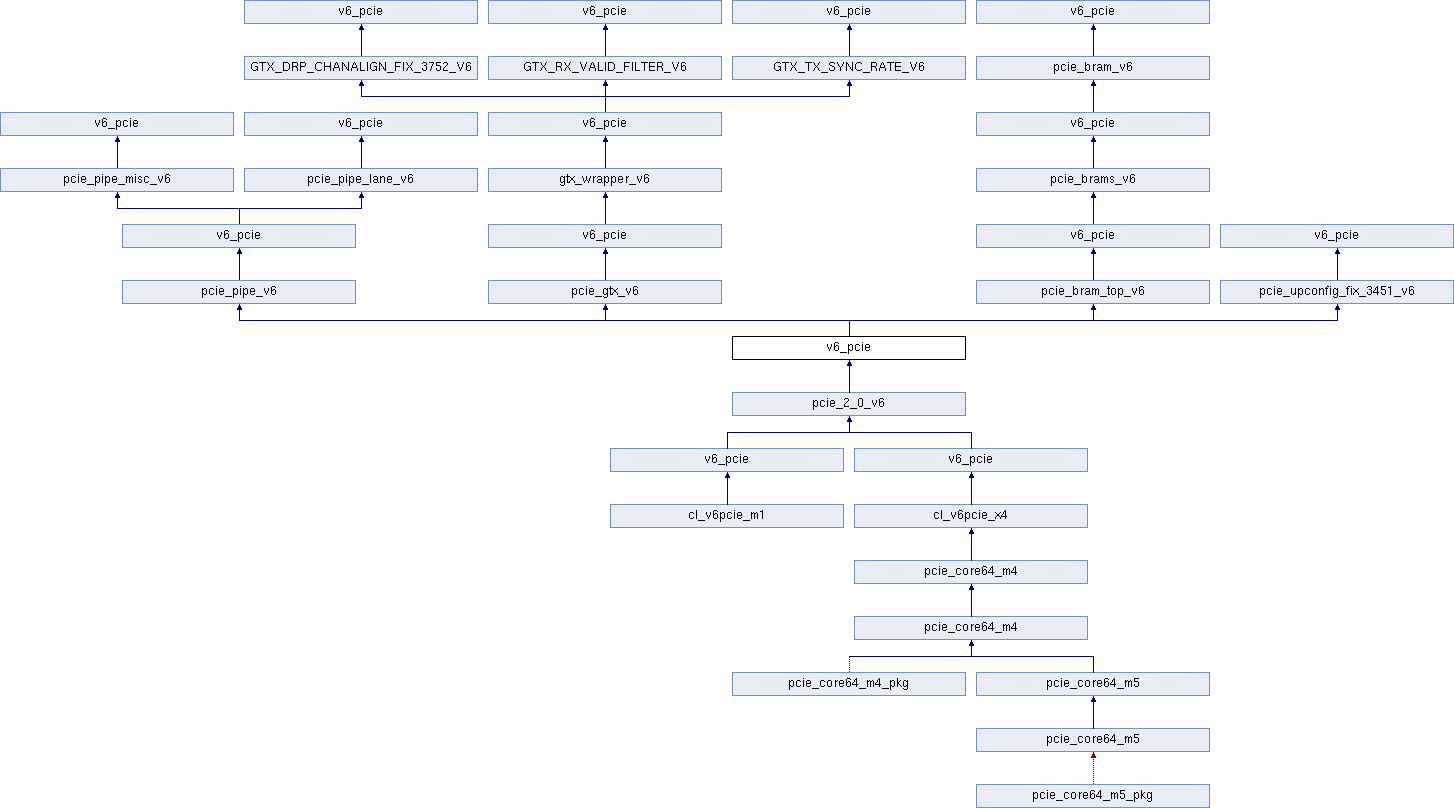

Граф наследования:v6_pcie:

Components | |

| pcie_pipe_v6 | <Entity pcie_pipe_v6> |

| pcie_gtx_v6 | <Entity pcie_gtx_v6> |

| pcie_bram_top_v6 | <Entity pcie_bram_top_v6> |

| pcie_upconfig_fix_3451_v6 | <Entity pcie_upconfig_fix_3451_v6> |

Signals | |

| LL2BADDLLPERRN | std_logic |

| LL2BADTLPERRN | std_logic |

| LL2PROTOCOLERRN | std_logic |

| LL2REPLAYROERRN | std_logic |

| LL2REPLAYTOERRN | std_logic |

| LL2SUSPENDOKN | std_logic |

| LL2TFCINIT1SEQN | std_logic |

| LL2TFCINIT2SEQN | std_logic |

| MIMRXRADDR | std_logic_vector ( 12 downto 0 ) |

| MIMRXRCE | std_logic |

| MIMRXREN | std_logic |

| MIMRXWADDR | std_logic_vector ( 12 downto 0 ) |

| MIMRXWDATA | std_logic_vector ( 67 downto 0 ) |

| MIMRXWDATA_tmp | std_logic_vector ( 71 downto 0 ) |

| MIMRXWEN | std_logic |

| MIMTXRADDR | std_logic_vector ( 12 downto 0 ) |

| MIMTXRCE | std_logic |

| MIMTXREN | std_logic |

| MIMTXWADDR | std_logic_vector ( 12 downto 0 ) |

| MIMTXWDATA | std_logic_vector ( 68 downto 0 ) |

| MIMTXWDATA_tmp | std_logic_vector ( 71 downto 0 ) |

| MIMTXWEN | std_logic |

| PIPERX0POLARITY | std_logic |

| PIPERX1POLARITY | std_logic |

| PIPERX2POLARITY | std_logic |

| PIPERX3POLARITY | std_logic |

| PIPERX4POLARITY | std_logic |

| PIPERX5POLARITY | std_logic |

| PIPERX6POLARITY | std_logic |

| PIPERX7POLARITY | std_logic |

| PIPETXDEEMPH | std_logic |

| PIPETXMARGIN | std_logic_vector ( 2 downto 0 ) |

| PIPETXRATE | std_logic |

| PIPETXRCVRDET | std_logic |

| PIPETXRESET | std_logic |

| PIPETX0CHARISK | std_logic_vector ( 1 downto 0 ) |

| PIPETX0COMPLIANCE | std_logic |

| PIPETX0DATA | std_logic_vector ( 15 downto 0 ) |

| PIPETX0ELECIDLE | std_logic |

| PIPETX0POWERDOWN | std_logic_vector ( 1 downto 0 ) |

| PIPETX1CHARISK | std_logic_vector ( 1 downto 0 ) |

| PIPETX1COMPLIANCE | std_logic |

| PIPETX1DATA | std_logic_vector ( 15 downto 0 ) |

| PIPETX1ELECIDLE | std_logic |

| PIPETX1POWERDOWN | std_logic_vector ( 1 downto 0 ) |

| PIPETX2CHARISK | std_logic_vector ( 1 downto 0 ) |

| PIPETX2COMPLIANCE | std_logic |

| PIPETX2DATA | std_logic_vector ( 15 downto 0 ) |

| PIPETX2ELECIDLE | std_logic |

| PIPETX2POWERDOWN | std_logic_vector ( 1 downto 0 ) |

| PIPETX3CHARISK | std_logic_vector ( 1 downto 0 ) |

| PIPETX3COMPLIANCE | std_logic |

| PIPETX3DATA | std_logic_vector ( 15 downto 0 ) |

| PIPETX3ELECIDLE | std_logic |

| PIPETX3POWERDOWN | std_logic_vector ( 1 downto 0 ) |

| PIPETX4CHARISK | std_logic_vector ( 1 downto 0 ) |

| PIPETX4COMPLIANCE | std_logic |

| PIPETX4DATA | std_logic_vector ( 15 downto 0 ) |

| PIPETX4ELECIDLE | std_logic |

| PIPETX4POWERDOWN | std_logic_vector ( 1 downto 0 ) |

| PIPETX5CHARISK | std_logic_vector ( 1 downto 0 ) |

| PIPETX5COMPLIANCE | std_logic |

| PIPETX5DATA | std_logic_vector ( 15 downto 0 ) |

| PIPETX5ELECIDLE | std_logic |

| PIPETX5POWERDOWN | std_logic_vector ( 1 downto 0 ) |

| PIPETX6CHARISK | std_logic_vector ( 1 downto 0 ) |

| PIPETX6COMPLIANCE | std_logic |

| PIPETX6DATA | std_logic_vector ( 15 downto 0 ) |

| PIPETX6ELECIDLE | std_logic |

| PIPETX6POWERDOWN | std_logic_vector ( 1 downto 0 ) |

| PIPETX7CHARISK | std_logic_vector ( 1 downto 0 ) |

| PIPETX7COMPLIANCE | std_logic |

| PIPETX7DATA | std_logic_vector ( 15 downto 0 ) |

| PIPETX7ELECIDLE | std_logic |

| PIPETX7POWERDOWN | std_logic_vector ( 1 downto 0 ) |

| PL2LINKUPN | std_logic |

| PL2RECEIVERERRN | std_logic |

| PL2RECOVERYN | std_logic |

| PL2RXELECIDLE | std_logic |

| PL2SUSPENDOK | std_logic |

| TL2ASPMSUSPENDCREDITCHECKOKN | std_logic |

| TL2ASPMSUSPENDREQN | std_logic |

| TL2PPMSUSPENDOKN | std_logic |

| LL2SENDASREQL1N | std_logic |

| LL2SENDENTERL1N | std_logic |

| LL2SENDENTERL23N | std_logic |

| LL2SUSPENDNOWN | std_logic |

| LL2TLPRCVN | std_logic |

| MIMRXRDATA | std_logic_vector ( 71 downto 0 ) |

| MIMTXRDATA | std_logic_vector ( 71 downto 0 ) |

| PL2DIRECTEDLSTATE | std_logic_vector ( 4 downto 0 ) |

| TL2ASPMSUSPENDCREDITCHECKN | std_logic |

| TL2PPMSUSPENDREQN | std_logic |

| PIPERX0CHANISALIGNED | std_logic |

| PIPERX0CHARISK | std_logic_vector ( 1 downto 0 ) |

| PIPERX0DATA | std_logic_vector ( 15 downto 0 ) |

| PIPERX0ELECIDLE | std_logic |

| PIPERX0PHYSTATUS | std_logic |

| PIPERX0STATUS | std_logic_vector ( 2 downto 0 ) |

| PIPERX0VALID | std_logic |

| PIPERX1CHANISALIGNED | std_logic |

| PIPERX1CHARISK | std_logic_vector ( 1 downto 0 ) |

| PIPERX1DATA | std_logic_vector ( 15 downto 0 ) |

| PIPERX1ELECIDLE | std_logic |

| PIPERX1PHYSTATUS | std_logic |

| PIPERX1STATUS | std_logic_vector ( 2 downto 0 ) |

| PIPERX1VALID | std_logic |

| PIPERX2CHANISALIGNED | std_logic |

| PIPERX2CHARISK | std_logic_vector ( 1 downto 0 ) |

| PIPERX2DATA | std_logic_vector ( 15 downto 0 ) |

| PIPERX2ELECIDLE | std_logic |

| PIPERX2PHYSTATUS | std_logic |

| PIPERX2STATUS | std_logic_vector ( 2 downto 0 ) |

| PIPERX2VALID | std_logic |

| PIPERX3CHANISALIGNED | std_logic |

| PIPERX3CHARISK | std_logic_vector ( 1 downto 0 ) |

| PIPERX3DATA | std_logic_vector ( 15 downto 0 ) |

| PIPERX3ELECIDLE | std_logic |

| PIPERX3PHYSTATUS | std_logic |

| PIPERX3STATUS | std_logic_vector ( 2 downto 0 ) |

| PIPERX3VALID | std_logic |

| PIPERX4CHANISALIGNED | std_logic |

| PIPERX4CHARISK | std_logic_vector ( 1 downto 0 ) |

| PIPERX4DATA | std_logic_vector ( 15 downto 0 ) |

| PIPERX4ELECIDLE | std_logic |

| PIPERX4PHYSTATUS | std_logic |

| PIPERX4STATUS | std_logic_vector ( 2 downto 0 ) |

| PIPERX4VALID | std_logic |

| PIPERX5CHANISALIGNED | std_logic |

| PIPERX5CHARISK | std_logic_vector ( 1 downto 0 ) |

| PIPERX5DATA | std_logic_vector ( 15 downto 0 ) |

| PIPERX5ELECIDLE | std_logic |

| PIPERX5PHYSTATUS | std_logic |

| PIPERX5STATUS | std_logic_vector ( 2 downto 0 ) |

| PIPERX5VALID | std_logic |

| PIPERX6CHANISALIGNED | std_logic |

| PIPERX6CHARISK | std_logic_vector ( 1 downto 0 ) |

| PIPERX6DATA | std_logic_vector ( 15 downto 0 ) |

| PIPERX6ELECIDLE | std_logic |

| PIPERX6PHYSTATUS | std_logic |

| PIPERX6STATUS | std_logic_vector ( 2 downto 0 ) |

| PIPERX6VALID | std_logic |

| PIPERX7CHANISALIGNED | std_logic |

| PIPERX7CHARISK | std_logic_vector ( 1 downto 0 ) |

| PIPERX7DATA | std_logic_vector ( 15 downto 0 ) |

| PIPERX7ELECIDLE | std_logic |

| PIPERX7PHYSTATUS | std_logic |

| PIPERX7STATUS | std_logic_vector ( 2 downto 0 ) |

| PIPERX7VALID | std_logic |

| PIPERX0POLARITYGT | std_logic |

| PIPERX1POLARITYGT | std_logic |

| PIPERX2POLARITYGT | std_logic |

| PIPERX3POLARITYGT | std_logic |

| PIPERX4POLARITYGT | std_logic |

| PIPERX5POLARITYGT | std_logic |

| PIPERX6POLARITYGT | std_logic |

| PIPERX7POLARITYGT | std_logic |

| PIPETXDEEMPHGT | std_logic |

| PIPETXMARGINGT | std_logic_vector ( 2 downto 0 ) |

| PIPETXRATEGT | std_logic |

| PIPETXRCVRDETGT | std_logic |

| PIPETX0CHARISKGT | std_logic_vector ( 1 downto 0 ) |

| PIPETX0COMPLIANCEGT | std_logic |

| PIPETX0DATAGT | std_logic_vector ( 15 downto 0 ) |

| PIPETX0ELECIDLEGT | std_logic |

| PIPETX0POWERDOWNGT | std_logic_vector ( 1 downto 0 ) |

| PIPETX1CHARISKGT | std_logic_vector ( 1 downto 0 ) |

| PIPETX1COMPLIANCEGT | std_logic |

| PIPETX1DATAGT | std_logic_vector ( 15 downto 0 ) |

| PIPETX1ELECIDLEGT | std_logic |

| PIPETX1POWERDOWNGT | std_logic_vector ( 1 downto 0 ) |

| PIPETX2CHARISKGT | std_logic_vector ( 1 downto 0 ) |

| PIPETX2COMPLIANCEGT | std_logic |

| PIPETX2DATAGT | std_logic_vector ( 15 downto 0 ) |

| PIPETX2ELECIDLEGT | std_logic |

| PIPETX2POWERDOWNGT | std_logic_vector ( 1 downto 0 ) |

| PIPETX3CHARISKGT | std_logic_vector ( 1 downto 0 ) |

| PIPETX3COMPLIANCEGT | std_logic |

| PIPETX3DATAGT | std_logic_vector ( 15 downto 0 ) |

| PIPETX3ELECIDLEGT | std_logic |

| PIPETX3POWERDOWNGT | std_logic_vector ( 1 downto 0 ) |

| PIPETX4CHARISKGT | std_logic_vector ( 1 downto 0 ) |

| PIPETX4COMPLIANCEGT | std_logic |

| PIPETX4DATAGT | std_logic_vector ( 15 downto 0 ) |

| PIPETX4ELECIDLEGT | std_logic |

| PIPETX4POWERDOWNGT | std_logic_vector ( 1 downto 0 ) |

| PIPETX5CHARISKGT | std_logic_vector ( 1 downto 0 ) |

| PIPETX5COMPLIANCEGT | std_logic |

| PIPETX5DATAGT | std_logic_vector ( 15 downto 0 ) |

| PIPETX5ELECIDLEGT | std_logic |

| PIPETX5POWERDOWNGT | std_logic_vector ( 1 downto 0 ) |

| PIPETX6CHARISKGT | std_logic_vector ( 1 downto 0 ) |

| PIPETX6COMPLIANCEGT | std_logic |

| PIPETX6DATAGT | std_logic_vector ( 15 downto 0 ) |

| PIPETX6ELECIDLEGT | std_logic |

| PIPETX6POWERDOWNGT | std_logic_vector ( 1 downto 0 ) |

| PIPETX7CHARISKGT | std_logic_vector ( 1 downto 0 ) |

| PIPETX7COMPLIANCEGT | std_logic |

| PIPETX7DATAGT | std_logic_vector ( 15 downto 0 ) |

| PIPETX7ELECIDLEGT | std_logic |

| PIPETX7POWERDOWNGT | std_logic_vector ( 1 downto 0 ) |

| PIPERX0CHANISALIGNEDGT | std_logic |

| PIPERX0CHARISKGT | std_logic_vector ( 1 downto 0 ) |

| PIPERX0DATAGT | std_logic_vector ( 15 downto 0 ) |

| PIPERX0ELECIDLEGT | std_logic |

| PIPERX0PHYSTATUSGT | std_logic |

| PIPERX0STATUSGT | std_logic_vector ( 2 downto 0 ) |

| PIPERX0VALIDGT | std_logic |

| PIPERX1CHANISALIGNEDGT | std_logic |

| PIPERX1CHARISKGT | std_logic_vector ( 1 downto 0 ) |

| PIPERX1DATAGT | std_logic_vector ( 15 downto 0 ) |

| PIPERX1ELECIDLEGT | std_logic |

| PIPERX1PHYSTATUSGT | std_logic |

| PIPERX1STATUSGT | std_logic_vector ( 2 downto 0 ) |

| PIPERX1VALIDGT | std_logic |

| PIPERX2CHANISALIGNEDGT | std_logic |

| PIPERX2CHARISKGT | std_logic_vector ( 1 downto 0 ) |

| PIPERX2DATAGT | std_logic_vector ( 15 downto 0 ) |

| PIPERX2ELECIDLEGT | std_logic |

| PIPERX2PHYSTATUSGT | std_logic |

| PIPERX2STATUSGT | std_logic_vector ( 2 downto 0 ) |

| PIPERX2VALIDGT | std_logic |

| PIPERX3CHANISALIGNEDGT | std_logic |

| PIPERX3CHARISKGT | std_logic_vector ( 1 downto 0 ) |

| PIPERX3DATAGT | std_logic_vector ( 15 downto 0 ) |

| PIPERX3ELECIDLEGT | std_logic |

| PIPERX3PHYSTATUSGT | std_logic |

| PIPERX3STATUSGT | std_logic_vector ( 2 downto 0 ) |

| PIPERX3VALIDGT | std_logic |

| PIPERX4CHANISALIGNEDGT | std_logic |

| PIPERX4CHARISKGT | std_logic_vector ( 1 downto 0 ) |

| PIPERX4DATAGT | std_logic_vector ( 15 downto 0 ) |

| PIPERX4ELECIDLEGT | std_logic |

| PIPERX4PHYSTATUSGT | std_logic |

| PIPERX4STATUSGT | std_logic_vector ( 2 downto 0 ) |

| PIPERX4VALIDGT | std_logic |

| PIPERX5CHANISALIGNEDGT | std_logic |

| PIPERX5CHARISKGT | std_logic_vector ( 1 downto 0 ) |

| PIPERX5DATAGT | std_logic_vector ( 15 downto 0 ) |

| PIPERX5ELECIDLEGT | std_logic |

| PIPERX5PHYSTATUSGT | std_logic |

| PIPERX5STATUSGT | std_logic_vector ( 2 downto 0 ) |

| PIPERX5VALIDGT | std_logic |

| PIPERX6CHANISALIGNEDGT | std_logic |

| PIPERX6CHARISKGT | std_logic_vector ( 1 downto 0 ) |

| PIPERX6DATAGT | std_logic_vector ( 15 downto 0 ) |

| PIPERX6ELECIDLEGT | std_logic |

| PIPERX6PHYSTATUSGT | std_logic |

| PIPERX6STATUSGT | std_logic_vector ( 2 downto 0 ) |

| PIPERX6VALIDGT | std_logic |

| PIPERX7CHANISALIGNEDGT | std_logic |

| PIPERX7CHARISKGT | std_logic_vector ( 1 downto 0 ) |

| PIPERX7DATAGT | std_logic_vector ( 15 downto 0 ) |

| PIPERX7ELECIDLEGT | std_logic |

| PIPERX7PHYSTATUSGT | std_logic |

| PIPERX7STATUSGT | std_logic_vector ( 2 downto 0 ) |

| PIPERX7VALIDGT | std_logic |

| filter_pipe_upconfig_fix_3451 | std_logic |

| PCIEXPTXN_v6pcie100 | std_logic_vector ( ( LINK_CAP_MAX_LINK_WIDTH_int- 1 ) downto 0 ) |

| PCIEXPTXP_v6pcie101 | std_logic_vector ( ( LINK_CAP_MAX_LINK_WIDTH_int- 1 ) downto 0 ) |

| TRNLNKUPN_v6pcie123 | std_logic |

| PHYRDYN_v6pcie102 | std_logic |

| USERRSTN_v6pcie139 | std_logic |

| RECEIVEDFUNCLVLRSTN_v6pcie116 | std_logic |

| LNKCLKEN_v6pcie97 | std_logic |

| TRNRBARHITN_v6pcie124 | std_logic_vector ( 6 downto 0 ) |

| TRNRD_v6pcie125 | std_logic_vector ( 63 downto 0 ) |

| TRNRECRCERRN_v6pcie126 | std_logic |

| TRNREOFN_v6pcie127 | std_logic |

| TRNRERRFWDN_v6pcie128 | std_logic |

| TRNRREMN_v6pcie129 | std_logic |

| TRNRSOFN_v6pcie130 | std_logic |

| TRNRSRCDSCN_v6pcie131 | std_logic |

| TRNRSRCRDYN_v6pcie132 | std_logic |

| TRNTBUFAV_v6pcie133 | std_logic_vector ( 5 downto 0 ) |

| TRNTCFGREQN_v6pcie134 | std_logic |

| TRNTDLLPDSTRDYN_v6pcie135 | std_logic |

| TRNTDSTRDYN_v6pcie136 | std_logic |

| TRNTERRDROPN_v6pcie137 | std_logic |

| TRNFCCPLD_v6pcie117 | std_logic_vector ( 11 downto 0 ) |

| TRNFCCPLH_v6pcie118 | std_logic_vector ( 7 downto 0 ) |

| TRNFCNPD_v6pcie119 | std_logic_vector ( 11 downto 0 ) |

| TRNFCNPH_v6pcie120 | std_logic_vector ( 7 downto 0 ) |

| TRNFCPD_v6pcie121 | std_logic_vector ( 11 downto 0 ) |

| TRNFCPH_v6pcie122 | std_logic_vector ( 7 downto 0 ) |

| CFGAERECRCCHECKEN_v6pcie0 | std_logic |

| CFGAERECRCGENEN_v6pcie1 | std_logic |

| CFGCOMMANDBUSMASTERENABLE_v6pcie2 | std_logic |

| CFGCOMMANDINTERRUPTDISABLE_v6pcie3 | std_logic |

| CFGCOMMANDIOENABLE_v6pcie4 | std_logic |

| CFGCOMMANDMEMENABLE_v6pcie5 | std_logic |

| CFGCOMMANDSERREN_v6pcie6 | std_logic |

| CFGDEVCONTROLAUXPOWEREN_v6pcie9 | std_logic |

| CFGDEVCONTROLCORRERRREPORTINGEN_v6pcie10 | std_logic |

| CFGDEVCONTROLENABLERO_v6pcie11 | std_logic |

| CFGDEVCONTROLEXTTAGEN_v6pcie12 | std_logic |

| CFGDEVCONTROLFATALERRREPORTINGEN_v6pcie13 | std_logic |

| CFGDEVCONTROLMAXPAYLOAD_v6pcie14 | std_logic_vector ( 2 downto 0 ) |

| CFGDEVCONTROLMAXREADREQ_v6pcie15 | std_logic_vector ( 2 downto 0 ) |

| CFGDEVCONTROLNONFATALREPORTINGEN_v6pcie16 | std_logic |

| CFGDEVCONTROLNOSNOOPEN_v6pcie17 | std_logic |

| CFGDEVCONTROLPHANTOMEN_v6pcie18 | std_logic |

| CFGDEVCONTROLURERRREPORTINGEN_v6pcie19 | std_logic |

| CFGDEVCONTROL2CPLTIMEOUTDIS_v6pcie7 | std_logic |

| CFGDEVCONTROL2CPLTIMEOUTVAL_v6pcie8 | std_logic_vector ( 3 downto 0 ) |

| CFGDEVSTATUSCORRERRDETECTED_v6pcie20 | std_logic |

| CFGDEVSTATUSFATALERRDETECTED_v6pcie21 | std_logic |

| CFGDEVSTATUSNONFATALERRDETECTED_v6pcie22 | std_logic |

| CFGDEVSTATUSURDETECTED_v6pcie23 | std_logic |

| CFGDO_v6pcie24 | std_logic_vector ( 31 downto 0 ) |

| CFGERRAERHEADERLOGSETN_v6pcie25 | std_logic |

| CFGERRCPLRDYN_v6pcie26 | std_logic |

| CFGINTERRUPTDO_v6pcie27 | std_logic_vector ( 7 downto 0 ) |

| CFGINTERRUPTMMENABLE_v6pcie28 | std_logic_vector ( 2 downto 0 ) |

| CFGINTERRUPTMSIENABLE_v6pcie29 | std_logic |

| CFGINTERRUPTMSIXENABLE_v6pcie30 | std_logic |

| CFGINTERRUPTMSIXFM_v6pcie31 | std_logic |

| CFGINTERRUPTRDYN_v6pcie32 | std_logic |

| CFGLINKCONTROLRCB_v6pcie41 | std_logic |

| CFGLINKCONTROLASPMCONTROL_v6pcie33 | std_logic_vector ( 1 downto 0 ) |

| CFGLINKCONTROLAUTOBANDWIDTHINTEN_v6pcie34 | std_logic |

| CFGLINKCONTROLBANDWIDTHINTEN_v6pcie35 | std_logic |

| CFGLINKCONTROLCLOCKPMEN_v6pcie36 | std_logic |

| CFGLINKCONTROLCOMMONCLOCK_v6pcie37 | std_logic |

| CFGLINKCONTROLEXTENDEDSYNC_v6pcie38 | std_logic |

| CFGLINKCONTROLHWAUTOWIDTHDIS_v6pcie39 | std_logic |

| CFGLINKCONTROLLINKDISABLE_v6pcie40 | std_logic |

| CFGLINKCONTROLRETRAINLINK_v6pcie42 | std_logic |

| CFGLINKSTATUSAUTOBANDWIDTHSTATUS_v6pcie43 | std_logic |

| CFGLINKSTATUSBANDWITHSTATUS_v6pcie44 | std_logic |

| CFGLINKSTATUSCURRENTSPEED_v6pcie45 | std_logic_vector ( 1 downto 0 ) |

| CFGLINKSTATUSDLLACTIVE_v6pcie46 | std_logic |

| CFGLINKSTATUSLINKTRAINING_v6pcie47 | std_logic |

| CFGLINKSTATUSNEGOTIATEDWIDTH_v6pcie48 | std_logic_vector ( 3 downto 0 ) |

| CFGMSGDATA_v6pcie49 | std_logic_vector ( 15 downto 0 ) |

| CFGMSGRECEIVED_v6pcie50 | std_logic |

| CFGMSGRECEIVEDASSERTINTA_v6pcie51 | std_logic |

| CFGMSGRECEIVEDASSERTINTB_v6pcie52 | std_logic |

| CFGMSGRECEIVEDASSERTINTC_v6pcie53 | std_logic |

| CFGMSGRECEIVEDASSERTINTD_v6pcie54 | std_logic |

| CFGMSGRECEIVEDDEASSERTINTA_v6pcie55 | std_logic |

| CFGMSGRECEIVEDDEASSERTINTB_v6pcie56 | std_logic |

| CFGMSGRECEIVEDDEASSERTINTC_v6pcie57 | std_logic |

| CFGMSGRECEIVEDDEASSERTINTD_v6pcie58 | std_logic |

| CFGMSGRECEIVEDERRCOR_v6pcie59 | std_logic |

| CFGMSGRECEIVEDERRFATAL_v6pcie60 | std_logic |

| CFGMSGRECEIVEDERRNONFATAL_v6pcie61 | std_logic |

| CFGMSGRECEIVEDPMASNAK_v6pcie62 | std_logic |

| CFGMSGRECEIVEDPMETO_v6pcie63 | std_logic |

| CFGMSGRECEIVEDPMETOACK_v6pcie64 | std_logic |

| CFGMSGRECEIVEDPMPME_v6pcie65 | std_logic |

| CFGMSGRECEIVEDSETSLOTPOWERLIMIT_v6pcie66 | std_logic |

| CFGMSGRECEIVEDUNLOCK_v6pcie67 | std_logic |

| CFGPCIELINKSTATE_v6pcie68 | std_logic_vector ( 2 downto 0 ) |

| CFGPMCSRPMEEN_v6pcie69 | std_logic |

| CFGPMCSRPMESTATUS_v6pcie70 | std_logic |

| CFGPMCSRPOWERSTATE_v6pcie71 | std_logic_vector ( 1 downto 0 ) |

| CFGPMRCVASREQL1N_v6pcie72 | std_logic |

| CFGPMRCVENTERL1N_v6pcie73 | std_logic |

| CFGPMRCVENTERL23N_v6pcie74 | std_logic |

| CFGPMRCVREQACKN_v6pcie75 | std_logic |

| CFGRDWRDONEN_v6pcie76 | std_logic |

| CFGSLOTCONTROLELECTROMECHILCTLPULSE_v6pcie77 | std_logic |

| CFGTRANSACTION_v6pcie78 | std_logic |

| CFGTRANSACTIONADDR_v6pcie79 | std_logic_vector ( 6 downto 0 ) |

| CFGTRANSACTIONTYPE_v6pcie80 | std_logic |

| CFGVCTCVCMAP_v6pcie81 | std_logic_vector ( 6 downto 0 ) |

| PLINITIALLINKWIDTH_v6pcie104 | std_logic_vector ( 2 downto 0 ) |

| PLLANEREVERSALMODE_v6pcie105 | std_logic_vector ( 1 downto 0 ) |

| PLLINKGEN2CAP_v6pcie106 | std_logic |

| PLLINKPARTNERGEN2SUPPORTED_v6pcie107 | std_logic |

| PLLINKUPCFGCAP_v6pcie108 | std_logic |

| PLLTSSMSTATE_v6pcie109 | std_logic_vector ( 5 downto 0 ) |

| PLPHYLNKUPN_v6pcie110 | std_logic |

| PLRECEIVEDHOTRST_v6pcie111 | std_logic |

| PLRXPMSTATE_v6pcie112 | std_logic_vector ( 1 downto 0 ) |

| PLSELLNKRATE_v6pcie113 | std_logic |

| PLSELLNKWIDTH_v6pcie114 | std_logic_vector ( 1 downto 0 ) |

| PLTXPMSTATE_v6pcie115 | std_logic_vector ( 2 downto 0 ) |

| DBGSCLRA_v6pcie82 | std_logic |

| DBGSCLRB_v6pcie83 | std_logic |

| DBGSCLRC_v6pcie84 | std_logic |

| DBGSCLRD_v6pcie85 | std_logic |

| DBGSCLRE_v6pcie86 | std_logic |

| DBGSCLRF_v6pcie87 | std_logic |

| DBGSCLRG_v6pcie88 | std_logic |

| DBGSCLRH_v6pcie89 | std_logic |

| DBGSCLRI_v6pcie90 | std_logic |

| DBGSCLRJ_v6pcie91 | std_logic |

| DBGSCLRK_v6pcie92 | std_logic |

| DBGVECA_v6pcie93 | std_logic_vector ( 63 downto 0 ) |

| DBGVECB_v6pcie94 | std_logic_vector ( 63 downto 0 ) |

| DBGVECC_v6pcie95 | std_logic_vector ( 11 downto 0 ) |

| PLDBGVEC_v6pcie103 | std_logic_vector ( 11 downto 0 ) |

| PCIEDRPDO_v6pcie98 | std_logic_vector ( 15 downto 0 ) |

| PCIEDRPDRDY_v6pcie99 | std_logic |

| GTPLLLOCK_v6pcie96 | std_logic |

| TxOutClk_v6pcie138 | std_logic |

| PIPERX0CHARISK_v6pcie | std_logic_vector ( 1 downto 0 ) |

| PIPERX1CHARISK_v6pcie | std_logic_vector ( 1 downto 0 ) |

| PIPERX2CHARISK_v6pcie | std_logic_vector ( 1 downto 0 ) |

| PIPERX3CHARISK_v6pcie | std_logic_vector ( 1 downto 0 ) |

| PIPERX4CHARISK_v6pcie | std_logic_vector ( 1 downto 0 ) |

| PIPERX5CHARISK_v6pcie | std_logic_vector ( 1 downto 0 ) |

| PIPERX6CHARISK_v6pcie | std_logic_vector ( 1 downto 0 ) |

| PIPERX7CHARISK_v6pcie | std_logic_vector ( 1 downto 0 ) |

Component Instantiations | |

| pcie_block_i | PCIE_2_0 |

| pcie_pipe_i | pcie_pipe_v6 <Entity pcie_pipe_v6> |

| pcie_gt_i | pcie_gtx_v6 <Entity pcie_gtx_v6> |

| pcie_bram_i | pcie_bram_top_v6 <Entity pcie_bram_top_v6> |

| pcie_upconfig_fix_3451_v6_i | pcie_upconfig_fix_3451_v6 <Entity pcie_upconfig_fix_3451_v6> |

Подробное описание

См. определение в файле pcie_2_0_v6.vhd строка 553

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/source_virtex6/pcie_2_0_v6.vhd

1.7.4

1.7.4