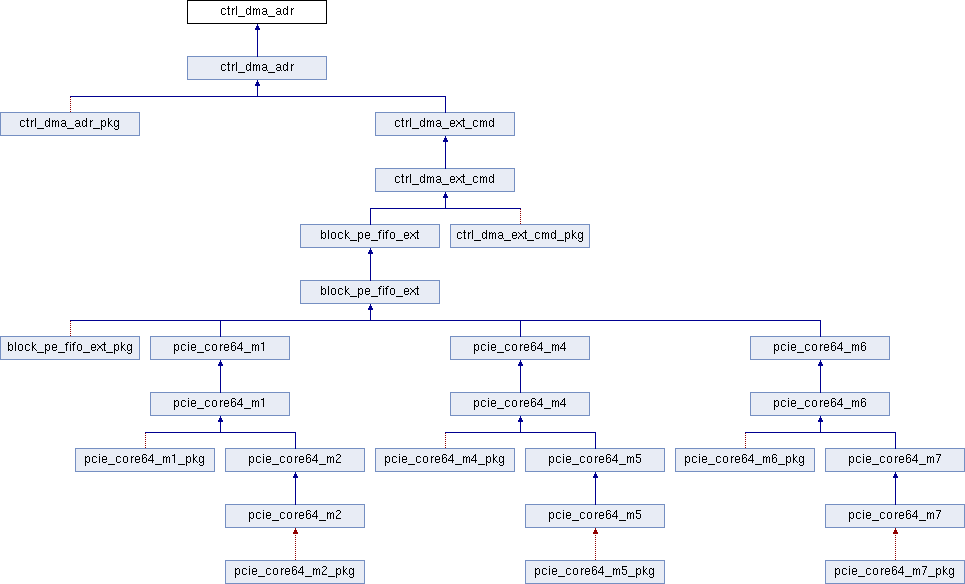

Граф наследования:ctrl_dma_adr:

Processes | |

| pr_adr | ( clk ) |

| pr_size | ( clk ) |

Signals | |

| port_a0 | std_logic_vector ( 17 downto 0 ) |

| port_b0 | std_logic_vector ( 17 downto 0 ) |

| port_c0 | std_logic_vector ( 47 downto 0 ) |

| port_p0 | std_logic_vector ( 47 downto 0 ) |

| opmode | std_logic_vector ( 6 downto 0 ) |

| carry0 | std_logic |

| port_a1 | std_logic_vector ( 17 downto 0 ) |

| port_b1 | std_logic_vector ( 17 downto 0 ) |

| port_c1 | std_logic_vector ( 47 downto 0 ) |

| port_p1 | std_logic_vector ( 47 downto 0 ) |

| carry1 | std_logic |

| subtract1 | std_logic |

| p2 | std_logic |

| n2 | std_logic |

| reg410_wr | std_logic |

| adr_low | std_logic_vector ( 2 downto 0 ) |

Component Instantiations | |

| dsp0 | DSP48 |

| dsp1 | DSP48 |

| ram0 | ram16x1d |

| ram1 | ram16x1d |

| ram2 | ram16x1d |

| ram_low | ram16x1d |

Подробное описание

См. определение в файле ctrl_dma_adr.vhd строка 102

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/pcie_fifo_ext/ctrl_dma_adr.vhd

1.7.4

1.7.4