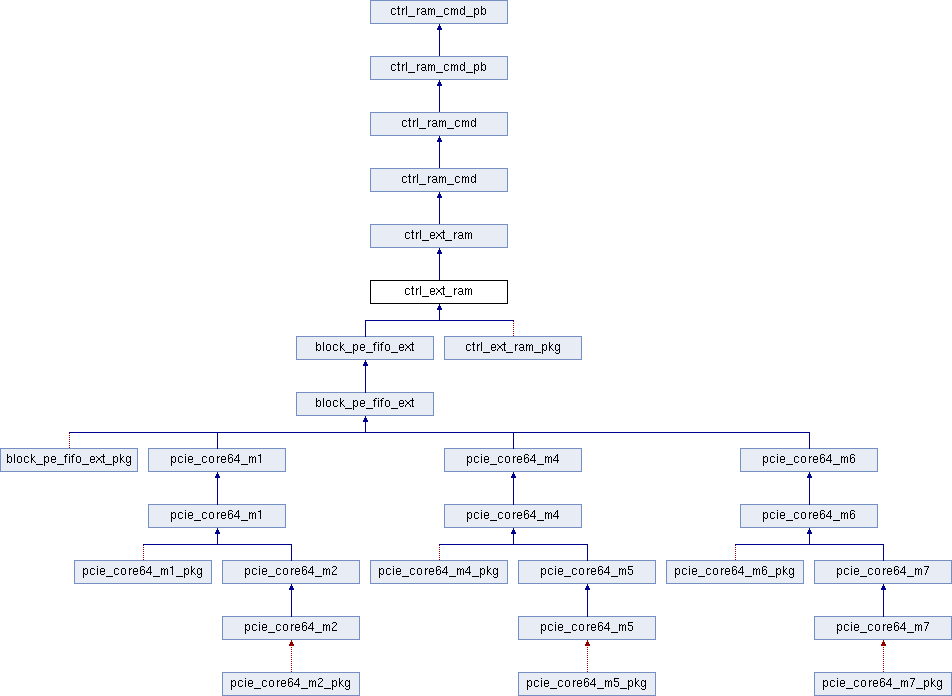

Граф наследования:ctrl_ext_ram:

Architectures | |

| ctrl_ext_ram | Architecture |

Libraries | |

| ieee | |

| unisim | |

| work | |

Packages | |

| std_logic_1164 | |

| std_logic_arith | |

| std_logic_unsigned | |

| vcomponents | |

| core64_type_pkg | Package <core64_type_pkg> |

| ctrl_ram_cmd_pkg | Package <ctrl_ram_cmd_pkg> |

Generics | |

| is_dsp48 | in integer := 1 |

Ports | |

| reset | in std_logic |

| clk | in std_logic |

| Тактовая частота ядра - 250 МГц | |

| aclk | in std_logic |

| Тактовая частота локальной шины - 266 МГц | |

| ram_change | in std_logic |

| loc_adr_we | in std_logic |

| data_in | in std_logic_vector ( 31 downto 0 ) |

| dma_chn | in std_logic |

| dma0_ctrl | in std_logic_vector ( 7 downto 0 ) |

| dma1_ctrl | in std_logic_vector ( 7 downto 0 ) |

| dma0_transfer_rdy | out std_logic |

| dma1_transfer_rdy | out std_logic |

| dma_wr_en | in std_logic |

| dma_wr | in std_logic |

| dma_wrdata | in std_logic_vector ( 63 downto 0 ) |

| dma_wraddr | in std_logic_vector ( 11 downto 0 ) |

| dma_rddata | out std_logic_vector ( 63 downto 0 ) |

| dma_rdaddr | in std_logic_vector ( 11 downto 0 ) |

| ext_fifo_disp | out type_ext_fifo_disp |

| запрос на доступ от узла EXT_FIFO. | |

| ext_fifo_disp_back | in type_ext_fifo_disp_back |

| ответ на запрос | |

Подробное описание

См. определение в файле ctrl_ext_ram.vhd строка 93

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/pcie_fifo_ext/ctrl_ext_ram.vhd

1.7.4

1.7.4