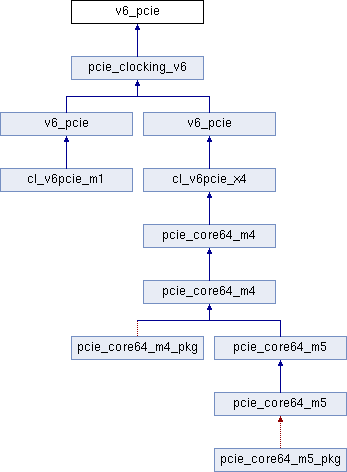

Граф наследования:v6_pcie:

Functions | |

| real | clkin_prd ( constant REF_CLK_FREQ: in integer ) |

| real | clkfb_mul ( constant REF_CLK_FREQ: in integer ) |

| integer | divclk_div ( constant REF_CLK_FREQ: in integer ) |

| integer | clk2_div ( constant LNK_WDT: in integer constant LNK_SPD: in integer constant USR_CLK_FREQ: in integer ) |

Processes | |

| PROCESS_65 | ( pipe_clk_v6pcie , gt_pll_lock ) |

Constants | |

| mmcm_clockin_period | real := clkin_prd ( REF_CLK_FREQ ) |

| mmcm_clockfb_mult | real := clkfb_mul ( REF_CLK_FREQ ) |

| mmcm_divclk_divide | integer := divclk_div ( REF_CLK_FREQ ) |

| mmcm_clock0_div | real := 4.0 |

| mmcm_clock1_div | integer := 8 |

| TCQ | integer := 1 |

| mmcm_clock2_div | integer := clk2_div ( CAP_LINK_WIDTH , CAP_LINK_SPEED , USER_CLK_FREQ ) |

| mmcm_clock3_div | integer := 2 |

Signals | |

| mmcm_locked | std_logic |

| mmcm_clkfbin | std_logic |

| mmcm_clkfbout | std_logic |

| mmcm_reset | std_logic |

| clk_500 | std_logic |

| clk_250 | std_logic |

| clk_125 | std_logic |

| user_clk_prebuf | std_logic |

| sel_lnk_rate_d | std_logic |

| reg_clock_locked | std_logic_vector ( 1 downto 0 ) := " 11 " |

| sys_clk_bufg_v6pcie3 | std_logic |

| pipe_clk_v6pcie | std_logic |

| user_clk_v6pcie4 | std_logic |

| block_clk_v6pcie0 | std_logic |

| drp_clk_v6pcie1 | std_logic |

| clock_locked_int | std_logic |

Component Instantiations | |

| pipe_clk_bufg | BUFG |

| sel_lnk_rate_delay | SRL16E |

| pipe_clk_bufgmux | BUFGMUX |

| user_clk_bufg | BUFG |

| block_clk_bufg | BUFG |

| drp_clk_bufg_i | BUFG |

| clkfbin_bufg_i | BUFG |

| sys_clk_bufg_i | BUFG |

| mmcm_adv_i | MMCM_ADV |

Подробное описание

См. определение в файле pcie_clocking_v6.vhd строка 89

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/source_virtex6/pcie_clocking_v6.vhd

1.7.4

1.7.4