Components | |

| ctrl_pcie_x8 | |

Signals | |

| trn_clk_c | std_logic |

| trn_reset_n_c | std_logic |

| trn_lnk_up_n_c | std_logic |

| cfg_trn_pending_n_c | std_logic |

| trn_tsof_n_c | std_logic |

| trn_teof_n_c | std_logic |

| trn_tsrc_rdy_n_c | std_logic |

| trn_tdst_rdy_n_c | std_logic |

| trn_tsrc_dsc_n_c | std_logic |

| trn_terrfwd_n_c | std_logic |

| trn_tdst_dsc_n_c | std_logic |

| trn_td_c | std_logic_vector ( ( 64 - 1 ) downto 0 ) |

| trn_trem_n_c | std_logic_vector ( 7 downto 0 ) |

| trn_tbuf_av_c | std_logic_vector ( ( 4 - 1 ) downto 0 ) |

| trn_rsof_n_c | std_logic |

| trn_reof_n_c | std_logic |

| trn_rsrc_rdy_n_c | std_logic |

| trn_rsrc_dsc_n_c | std_logic |

| trn_rdst_rdy_n_c | std_logic |

| trn_rerrfwd_n_c | std_logic |

| trn_rnp_ok_n_c | std_logic |

| trn_rd_c | std_logic_vector ( ( 64 - 1 ) downto 0 ) |

| trn_rrem_n_c | std_logic_vector ( 7 downto 0 ) |

| trn_rbar_hit_n_c | std_logic_vector ( 6 downto 0 ) |

| trn_rfc_nph_av_c | std_logic_vector ( 7 downto 0 ) |

| trn_rfc_npd_av_c | std_logic_vector ( 11 downto 0 ) |

| trn_rfc_ph_av_c | std_logic_vector ( 7 downto 0 ) |

| trn_rfc_pd_av_c | std_logic_vector ( 11 downto 0 ) |

| trn_rcpl_streaming_n_c | std_logic |

| cfg_do_c | std_logic_vector ( 31 downto 0 ) |

| cfg_di_c | std_logic_vector ( 31 downto 0 ) |

| cfg_dwaddr_c | std_logic_vector ( 9 downto 0 ) |

| cfg_byte_en_n_c | std_logic_vector ( 3 downto 0 ) |

| cfg_err_tlp_cpl_header_c | std_logic_vector ( 47 downto 0 ) |

| cfg_wr_en_n_c | std_logic |

| cfg_rd_en_n_c | std_logic |

| cfg_rd_wr_done_n_c | std_logic |

| cfg_err_cor_n_c | std_logic |

| cfg_err_ur_n_c | std_logic |

| cfg_err_ecrc_n_c | std_logic |

| cfg_err_cpl_timeout_n_c | std_logic |

| cfg_err_cpl_abort_n_c | std_logic |

| cfg_err_cpl_unexpect_n_c | std_logic |

| cfg_err_posted_n_c | std_logic |

| cfg_err_cpl_rdy_n_c | std_logic |

| cfg_interrupt_n_c | std_logic |

| cfg_interrupt_rdy_n_c | std_logic |

| cfg_interrupt_assert_n_c | std_logic |

| cfg_interrupt_di_c | std_logic_vector ( 7 downto 0 ) |

| cfg_interrupt_do_c | std_logic_vector ( 7 downto 0 ) |

| cfg_interrupt_mmenable_c | std_logic_vector ( 2 downto 0 ) |

| cfg_interrupt_msienable_c | std_logic |

| cfg_turnoff_ok_n_c | std_logic |

| cfg_to_turnoff_n_c | std_logic |

| cfg_pm_wake_n_c | std_logic |

| cfg_pcie_link_state_n_c | std_logic_vector ( 2 downto 0 ) |

| cfg_bus_number_c | std_logic_vector ( 7 downto 0 ) |

| cfg_device_number_c | std_logic_vector ( 4 downto 0 ) |

| cfg_function_number_c | std_logic_vector ( 2 downto 0 ) |

| cfg_status_c | std_logic_vector ( 15 downto 0 ) |

| cfg_command_c | std_logic_vector ( 15 downto 0 ) |

| cfg_dstatus_c | std_logic_vector ( 15 downto 0 ) |

| cfg_dcommand_c | std_logic_vector ( 15 downto 0 ) |

| cfg_lstatus_c | std_logic_vector ( 15 downto 0 ) |

| cfg_lcommand_c | std_logic_vector ( 15 downto 0 ) |

| vector_fast_simulation | std_logic_vector ( 0 downto 0 ) := ( 0 = > ' 1 ' ) |

| refclkout | std_logic |

| clk | std_logic |

| rstp | std_logic |

| trn_rx | type_trn_rx |

| приём пакета | |

| trn_rx_back | type_trn_rx_back |

| готовность к приёму пакета | |

| reg_access | type_reg_access |

| запрос на доступ к регистрам | |

| rx_tx_engine | type_rx_tx_engine |

| обмен RX->TX. | |

| tx_rx_engine | type_tx_rx_engine |

| обмен TX->RX. | |

| rx_ext_fifo | type_rx_ext_fifo |

| обмен RX->EXT_FIFO. | |

| tx_ext_fifo | type_tx_ext_fifo |

| tx_ext_fifo_back | type_tx_ext_fifo_back |

| reg_access_back | type_reg_access_back |

| completer_id | std_logic_vector ( 15 downto 0 ) |

| trn_tx | type_trn_tx |

| trn_tx_back | type_trn_tx_back |

| reg_disp | type_reg_disp |

| reg_disp_back | type_reg_disp_back |

| reg_ext_fifo | type_reg_ext_fifo |

| reg_ext_fifo_back | type_reg_ext_fifo_back |

| ext_fifo_disp | type_ext_fifo_disp |

| запрос на доступ от узла EXT_FIFO. | |

| ext_fifo_disp_back | type_ext_fifo_disp_back |

| ответ на запрос | |

| pb_rstp | std_logic |

| irq | std_logic |

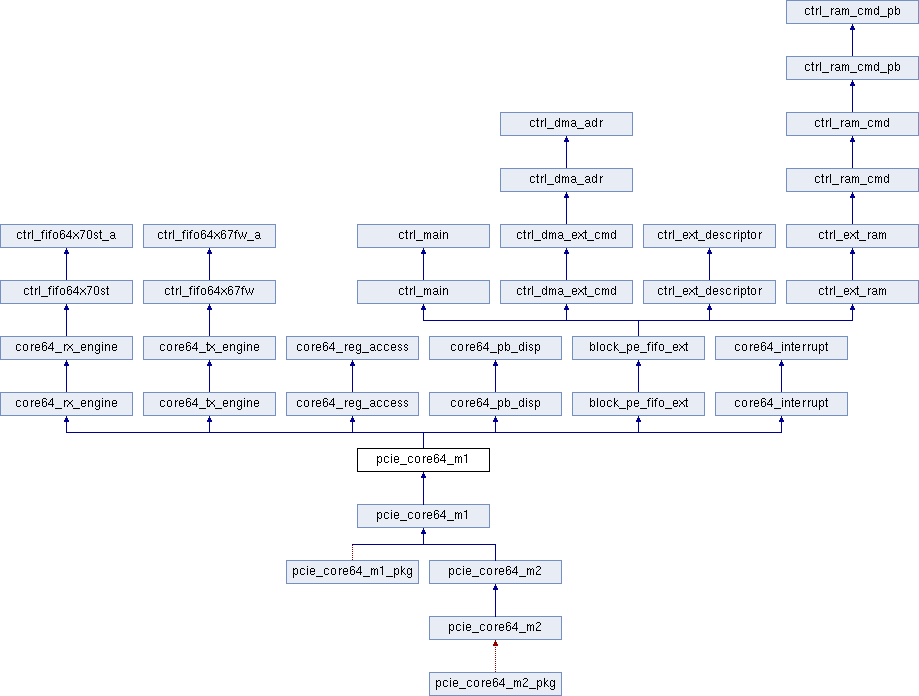

Component Instantiations | |

| ep | ctrl_pcie_x8 |

| rx | core64_rx_engine <Entity core64_rx_engine> |

| tx | core64_tx_engine <Entity core64_tx_engine> |

| 1 - сброс | |

| reg | core64_reg_access <Entity core64_reg_access> |

| 1 - сброс | |

| disp | core64_pb_disp <Entity core64_pb_disp> |

| 1 - сброс | |

| fifo | block_pe_fifo_ext <Entity block_pe_fifo_ext> |

| 1 - сброс | |

| int | core64_interrupt <Entity core64_interrupt> |

Подробное описание

См. определение в файле pcie_core64_m1.vhd строка 144

Данные класса

disp core64_pb_disp [Component Instantiation] |

1 - сброс

тактовая частота ядра - 250 MHz запрос на доступ к регистрам ответ на запрос запрос на доступ к регистрам из BAR1 ответ на запрос запрос на доступ к блокам управления EXT_FIFO ответ на запрос шина данных - выход шина данных - вход адрес регистра 1 - запись в регистры 1 - чтение из регистров блока номер блока для чтения 1 - запись в регистр по адресам 0x100000 - 0x1FFFFF 1 - чтение из регистра по адресам 0x100000 - 0x1FFFFF 1 - запрос прерывания

См. определение в файле pcie_core64_m1.vhd строка 592

fifo block_pe_fifo_ext [Component Instantiation] |

1 - сброс

тактовая частота ядра - 250 MHz запрос на доступ к регистрам из BAR1 ответ на запрос запрос на доступ от узла EXT_FIFO ответ на запрос тактовая частота локальной шины - 266 МГц запрос ответ

См. определение в файле pcie_core64_m1.vhd строка 615

reg core64_reg_access [Component Instantiation] |

1 - сброс

тактовая частота ядра - 250 MHz передача пакета готовность к передаче пакета идентификатор устройства запрос на доступ к регистрам обмен RX->TX обмен TX->RX обмен TX->EXT_FIFO обмен TX->EXT_FIFO

См. определение в файле pcie_core64_m1.vhd строка 559

tx core64_tx_engine [Component Instantiation] |

1 - сброс

тактовая частота ядра - 250 MHz приём пакета готовность к приёму пакета запрос на доступ к регистрам обмен RX->TX обмен TX->RX обмен RX->EXT_FIFO

См. определение в файле pcie_core64_m1.vhd строка 532

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/top/pcie_core64_m1.vhd

1.7.4

1.7.4