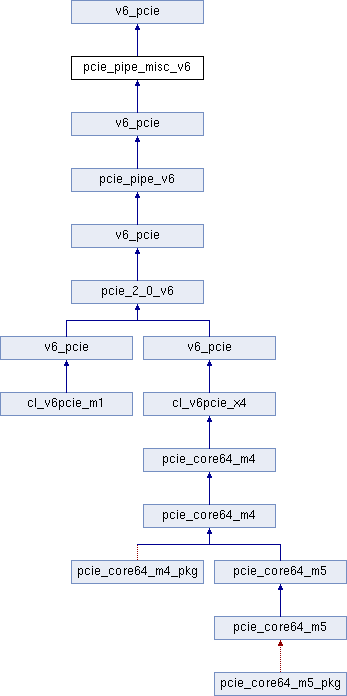

Граф наследования:pcie_pipe_misc_v6:

Architectures | |

| v6_pcie | Architecture |

Libraries | |

| ieee | |

Packages | |

| std_logic_1164 | |

Generics | |

| PIPE_PIPELINE_STAGES | integer := 0 |

Ports | |

| pipe_tx_rcvr_det_i | in std_logic |

| pipe_tx_reset_i | in std_logic |

| pipe_tx_rate_i | in std_logic |

| pipe_tx_deemph_i | in std_logic |

| pipe_tx_margin_i | in std_logic_vector ( 2 downto 0 ) |

| pipe_tx_swing_i | in std_logic |

| pipe_tx_rcvr_det_o | out std_logic |

| pipe_tx_reset_o | out std_logic |

| pipe_tx_rate_o | out std_logic |

| pipe_tx_deemph_o | out std_logic |

| pipe_tx_margin_o | out std_logic_vector ( 2 downto 0 ) |

| pipe_tx_swing_o | out std_logic |

| pipe_clk | in std_logic |

| rst_n | in std_logic |

Подробное описание

См. определение в файле pcie_pipe_misc_v6.vhd строка 62

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/source_virtex6/pcie_pipe_misc_v6.vhd

1.7.4

1.7.4