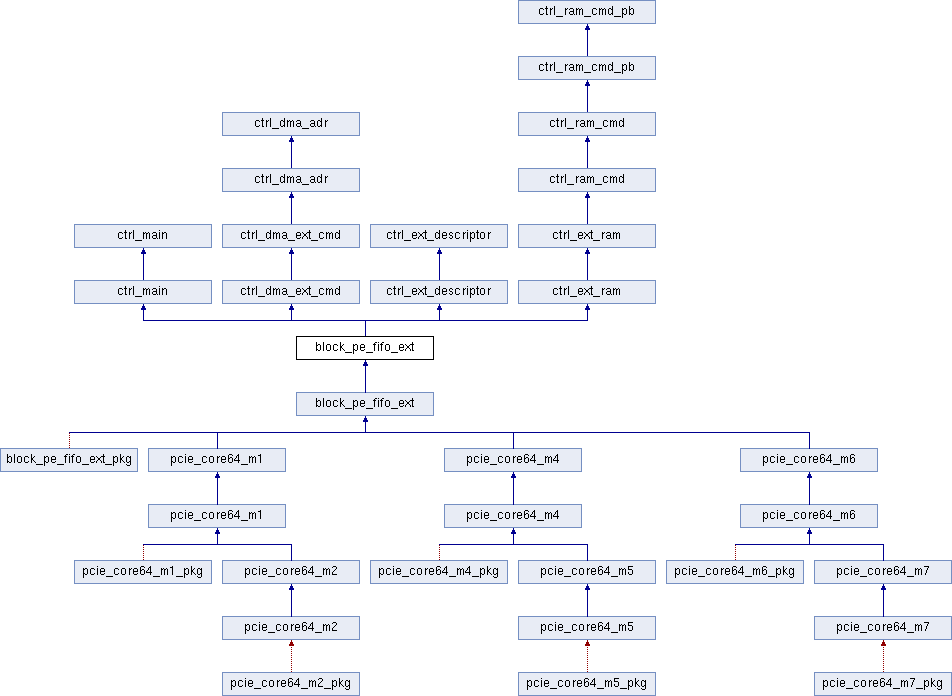

Граф наследования:block_pe_fifo_ext:

Processes | |

| pr_dma_ctrl | ( clk ) |

Components | |

| kcpsm3 | |

| p_fifo | |

Signals | |

| ram_adra | std_logic_vector ( 8 downto 0 ) |

| ram_adrb | std_logic_vector ( 8 downto 0 ) |

| ram_di_a | std_logic_vector ( 31 downto 0 ) |

| ram_do_a | std_logic_vector ( 31 downto 0 ) |

| ram_we_a | std_logic |

| ram_do_b | std_logic_vector ( 31 downto 0 ) |

| reg_dma0_status | std_logic_vector ( 15 downto 0 ) |

| reg_dma1_status | std_logic_vector ( 15 downto 0 ) |

| address | std_logic_vector ( 9 downto 0 ) |

| instruction | std_logic_vector ( 17 downto 0 ) |

| port_id | std_logic_vector ( 7 downto 0 ) |

| write_strobe | std_logic |

| read_strobe | std_logic |

| interrupt | std_logic |

| interrupt_ack | std_logic |

| kc_reset | std_logic |

| in_port | std_logic_vector ( 7 downto 0 ) |

| out_port | std_logic_vector ( 7 downto 0 ) |

| reg4_do | std_logic_vector ( 7 downto 0 ) |

| reg8_do | std_logic_vector ( 7 downto 0 ) |

| ram0_wr | std_logic |

| ram1_wr | std_logic |

| ram_adr | std_logic_vector ( 10 downto 0 ) |

| reg_dma_chn | std_logic_vector ( 1 downto 0 ) |

| reg_status | std_logic_vector ( 7 downto 0 ) |

| reg_dma_status | std_logic_vector ( 3 downto 0 ) |

| reg_descriptor_status | std_logic_vector ( 1 downto 0 ) |

| dsc_adr_h | std_logic_vector ( 7 downto 0 ) |

| dsc_adr | std_logic_vector ( 23 downto 0 ) |

| dsc_size | std_logic_vector ( 23 downto 0 ) |

| dma0_rs0 | std_logic_vector ( 7 downto 0 ) |

| dma1_rs0 | std_logic_vector ( 7 downto 0 ) |

| dma0_rs0x | std_logic_vector ( 7 downto 0 ) |

| dma1_rs0x | std_logic_vector ( 7 downto 0 ) |

| dma_rs0 | std_logic_vector ( 7 downto 0 ) |

| reg_test | std_logic_vector ( 7 downto 0 ) |

| dx | std_logic_vector ( 7 downto 0 ) |

| ram_transfer_rdy | std_logic |

| dma0_transfer_rdy | std_logic |

| dma1_transfer_rdy | std_logic |

| dma0_eot_clr | std_logic |

| dma1_eot_clr | std_logic |

| dma0_ctrl | std_logic_vector ( 7 downto 0 ) |

| dma1_ctrl | std_logic_vector ( 7 downto 0 ) |

| ram_change | std_logic |

| reg_dma0_ctrl | std_logic_vector ( 7 downto 0 ) |

| reg_dma1_ctrl | std_logic_vector ( 7 downto 0 ) |

| reg_dma0_mode | std_logic_vector ( 7 downto 0 ) |

| reg_dma1_mode | std_logic_vector ( 7 downto 0 ) |

| dsc_correct | std_logic |

| dsc_cmd | std_logic_vector ( 7 downto 0 ) |

| dsc_change_adr | std_logic |

| dsc_change_mode | std_logic |

| dsc_load_en | std_logic |

| dma_reg0 | std_logic_vector ( 2 downto 0 ) |

| dma_change_adr | std_logic |

| dma_cmd_status | std_logic_vector ( 2 downto 0 ) |

| dma_chn | std_logic |

| pci_adr_we | std_logic |

| pci_adr_h_we | std_logic |

| loc_adr_we | std_logic |

| ack_cnt | std_logic_vector ( 4 downto 0 ) |

| reset | std_logic |

| dma_wraddr | std_logic_vector ( 11 downto 0 ) |

| dma_rdaddr | std_logic_vector ( 11 downto 0 ) |

| dma_wrdata | std_logic_vector ( 63 downto 0 ) |

Component Instantiations | |

| ram | RAMB16_S36_S36 |

| main | ctrl_main <Entity ctrl_main> |

| cmd | ctrl_dma_ext_cmd <Entity ctrl_dma_ext_cmd> |

| dsc | ctrl_ext_descriptor <Entity ctrl_ext_descriptor> |

| ram_data | ctrl_ext_ram <Entity ctrl_ext_ram> |

Подробное описание

См. определение в файле block_pe_fifo_ext.vhd строка 156

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/pcie_fifo_ext/block_pe_fifo_ext.vhd

1.7.4

1.7.4