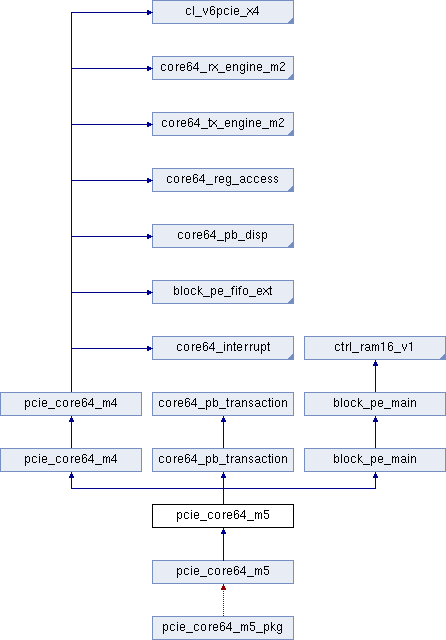

Граф наследования:pcie_core64_m5:

Signals | |

| bp_host_data | std_logic_vector ( 31 downto 0 ) |

| шина данных - выход | |

| bp_data | std_logic_vector ( 31 downto 0 ) |

| шина данных - вход | |

| bp_adr | std_logic_vector ( 19 downto 0 ) |

| адрес регистра внутри блока | |

| bp_we | std_logic_vector ( 3 downto 0 ) |

| 1 - запись в регистры | |

| bp_rd | std_logic_vector ( 3 downto 0 ) |

| 1 - чтение из регистров блока | |

| bp_sel | std_logic_vector ( 1 downto 0 ) |

| номер блока для чтения | |

| bp_reg_we | std_logic |

| 1 - запись в регистр по адресам 0x100000 - 0x1FFFFF | |

| bp_reg_rd | std_logic |

| 1 - чтение из регистра по адресам 0x100000 - 0x1FFFFF | |

| bp_irq | std_logic |

| 1 - запрос прерывания | |

| clk250 | std_logic |

| reset | std_logic |

| pb_master | type_pb_master |

| запрос | |

| pb_slave | type_pb_slave |

| ответ | |

| pb_reset | std_logic |

| brd_mode | std_logic_vector ( 15 downto 0 ) |

| bp0_data | std_logic_vector ( 31 downto 0 ) |

Component Instantiations | |

| core | pcie_core64_m4 <Entity pcie_core64_m4> |

| tz | core64_pb_transaction <Entity core64_pb_transaction> |

| Значение опорной тактовой частоты [МГц]. | |

| main | block_pe_main <Entity block_pe_main> |

| 0 - сброс | |

Подробное описание

См. определение в файле pcie_core64_m5.vhd строка 146

Данные класса

main block_pe_main [Component Instantiation] |

0 - сброс

тактовая частота локальной шины - 266 МГц запрос ответ

Переопределяет метод предка block_pe_fifo_ext.

См. определение в файле pcie_core64_m5.vhd строка 248

tz core64_pb_transaction [Component Instantiation] |

Значение опорной тактовой частоты [МГц].

0 - синтез, 1 - моделирование

См. определение в файле pcie_core64_m5.vhd строка 228

Объявления и описания членов класса находятся в файле:

- pcie_src/components/pcie_core/pcie_core64_m5.vhd

1.7.4

1.7.4