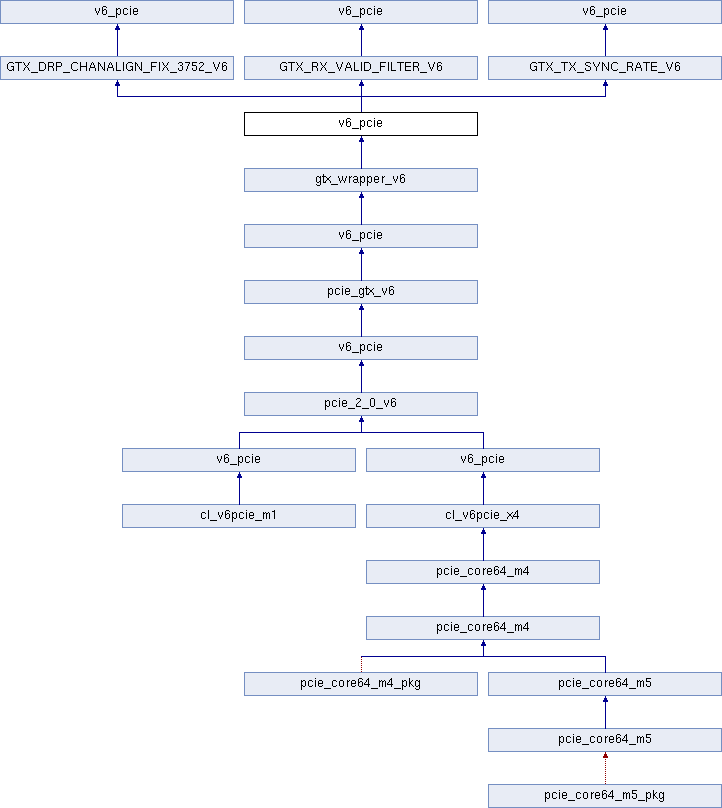

Граф наследования:v6_pcie:

Functions | |

| std_logic_vector | to_stdlogicvector ( val_in: in integer , length: in integer ) |

| std_logic | and_bw ( val_in: in std_logic_vector ) |

| integer | to_integer ( in_val: in boolean ) |

| std_logic | to_stdlogic ( in_val: in boolean ) |

| bit_vector | pll_cp_cfg_sel ( ref_freq: in integer ) |

| integer | clk_div ( in_val: in integer ) |

| integer | pll_div ( in_val: in integer ) |

Processes | |

| PROCESS_59 | ( PCLK ) |

Components | |

| GTX_RX_VALID_FILTER_V6 | <Entity GTX_RX_VALID_FILTER_V6> |

| GTX_DRP_CHANALIGN_FIX_3752_V6 | <Entity GTX_DRP_CHANALIGN_FIX_3752_V6> |

| GTX_TX_SYNC_RATE_V6 | <Entity GTX_TX_SYNC_RATE_V6> |

Types | |

| type_v6pcie10 | array ( NO_OF_LANES+ 1 downto 0 ) of std_logic_vector ( 3 downto 0 ) |

| type_v6pcie11 | array ( NO_OF_LANES- 1 downto 0 ) of std_logic |

| type_v6pcie16 | array ( NO_OF_LANES- 1 downto 0 ) of std_logic_vector ( 12 downto 0 ) |

Signals | |

| tied_to_ground_i | std_logic |

| tied_to_ground_vec_i | std_logic_vector ( 31 downto 0 ) |

| tied_to_vcc_i | std_logic |

| RxData_dummy | std_logic_vector ( 15 downto 0 ) |

| RxDataK_dummy | std_logic_vector ( 1 downto 0 ) |

| TxData_dummy | std_logic_vector ( 15 downto 0 ) |

| TxDataK_dummy | std_logic_vector ( 1 downto 0 ) |

| GTX_TxData | std_logic_vector ( ( NO_OF_LANES * 16 ) - 1 downto 0 ) |

| GTX_TxDataK | std_logic_vector ( ( NO_OF_LANES * 2 ) - 1 downto 0 ) |

| GTX_TxElecIdle | std_logic_vector ( ( NO_OF_LANES ) - 1 downto 0 ) |

| GTX_TxCompliance | std_logic_vector ( ( NO_OF_LANES- 1 ) downto 0 ) |

| GTX_RXP | std_logic_vector ( ( NO_OF_LANES ) - 1 downto 0 ) |

| GTX_RXN | std_logic_vector ( ( NO_OF_LANES ) - 1 downto 0 ) |

| GTX_TXP | std_logic_vector ( ( NO_OF_LANES ) - 1 downto 0 ) |

| GTX_TXN | std_logic_vector ( ( NO_OF_LANES ) - 1 downto 0 ) |

| GTX_RxData | std_logic_vector ( ( NO_OF_LANES * 16 ) - 1 downto 0 ) |

| GTX_RxDataK | std_logic_vector ( ( NO_OF_LANES * 2 ) - 1 downto 0 ) |

| GTX_RxPolarity | std_logic_vector ( ( NO_OF_LANES ) - 1 downto 0 ) |

| GTX_RxValid | std_logic_vector ( ( NO_OF_LANES ) - 1 downto 0 ) |

| GTX_RxElecIdle | std_logic_vector ( ( NO_OF_LANES ) - 1 downto 0 ) |

| GTX_RxResetDone | std_logic_vector ( ( NO_OF_LANES- 1 ) downto 0 ) |

| GTX_RxChbondLevel | std_logic_vector ( ( NO_OF_LANES * 3 ) - 1 downto 0 ) |

| GTX_RxStatus | std_logic_vector ( ( NO_OF_LANES * 3 ) - 1 downto 0 ) |

| RXCHBOND | type_v6pcie10 |

| TXBYPASS8B10B | std_logic_vector ( 3 downto 0 ) |

| RXDEC8B10BUSE | std_logic |

| GTX_PhyStatus | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| RESETDONE | type_v6pcie11 |

| GTXRESET | std_logic |

| RXRECCLK | std_logic |

| SYNC_DONE | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| OUT_DIV_RESET | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| PCS_RESET | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| TXENPMAPHASEALIGN | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| TXPMASETPHASE | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| TXRESETDONE | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| TXRATEDONE | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| PHYSTATUS_int | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| RATE_CLK_SEL | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| TXOCLK | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| TXDLYALIGNDISABLE | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| TXDLYALIGNRESET | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| GTX_RxResetDone_q | std_logic_vector ( ( NO_OF_LANES- 1 ) downto 0 ) |

| TXRESETDONE_q | std_logic_vector ( ( NO_OF_LANES- 1 ) downto 0 ) |

| daddr | std_logic_vector ( ( NO_OF_LANES * 8 - 1 ) downto 0 ) |

| den | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| din | std_logic_vector ( ( NO_OF_LANES * 16 - 1 ) downto 0 ) |

| dwe | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| drpstate | std_logic_vector ( ( NO_OF_LANES * 4 - 1 ) downto 0 ) |

| drdy | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| dout | std_logic_vector ( ( NO_OF_LANES * 16 - 1 ) downto 0 ) |

| write_drp_cb_fts | std_logic |

| write_drp_cb_ts1 | std_logic |

| v6pcie12 | std_logic |

| v6pcie13 | std_logic |

| v6pcie14 | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| v6pcie15 | std_logic |

| v6pcie16 | type_v6pcie16 |

| v6pcie18 | std_logic_vector ( 1 downto 0 ) |

| v6pcie21 | std_logic_vector ( ( NO_OF_LANES * 4 ) - 1 downto 0 ) |

| v6pcie23 | std_logic_vector ( ( NO_OF_LANES * 32 ) - 1 downto 0 ) |

| v6pcie24 | std_logic_vector ( 1 downto 0 ) |

| v6pcie25 | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| v6pcie26 | std_logic_vector ( 19 downto 0 ) |

| v6pcie27 | std_logic_vector ( ( NO_OF_LANES * 4 ) - 1 downto 0 ) |

| v6pcie28 | std_logic_vector ( ( NO_OF_LANES * 4 ) - 1 downto 0 ) |

| v6pcie29 | std_logic_vector ( ( NO_OF_LANES * 32 ) - 1 downto 0 ) := ( others = > ' 0 ' ) |

| v6pcie30 | std_logic_vector ( 2 downto 0 ) |

| RxData_v6pcie3 | std_logic_vector ( ( NO_OF_LANES * 16 ) - 1 downto 0 ) |

| RxDataK_v6pcie4 | std_logic_vector ( ( NO_OF_LANES * 2 ) - 1 downto 0 ) |

| RxValid_v6pcie8 | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| RxElecIdle_v6pcie5 | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| RxStatus_v6pcie7 | std_logic_vector ( ( NO_OF_LANES * 3 ) - 1 downto 0 ) |

| RxPLLLkDet_v6pcie6 | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| PhyStatus_v6pcie1 | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

| ChanIsAligned_v6pcie0 | std_logic_vector ( NO_OF_LANES- 1 downto 0 ) |

Component Instantiations | |

| GTX_DRP_CHANALIGN_FIX_3752 | GTX_DRP_CHANALIGN_FIX_3752_V6 <Entity GTX_DRP_CHANALIGN_FIX_3752_V6> |

| GTX_RX_VALID_FILTER | GTX_RX_VALID_FILTER_V6 <Entity GTX_RX_VALID_FILTER_V6> |

| GTX_TX_SYNC | GTX_TX_SYNC_RATE_V6 <Entity GTX_TX_SYNC_RATE_V6> |

| GTX | GTXE1 |

Подробное описание

См. определение в файле gtx_wrapper_v6.vhd строка 121

Объявления и описания членов класса находятся в файле:

- pcie_src/pcie_core64_m1/source_virtex6/gtx_wrapper_v6.vhd

1.7.4

1.7.4